5 assignment of devicenet addresses – IAI America E-Con User Manual

Page 86

78

6. SCON-C

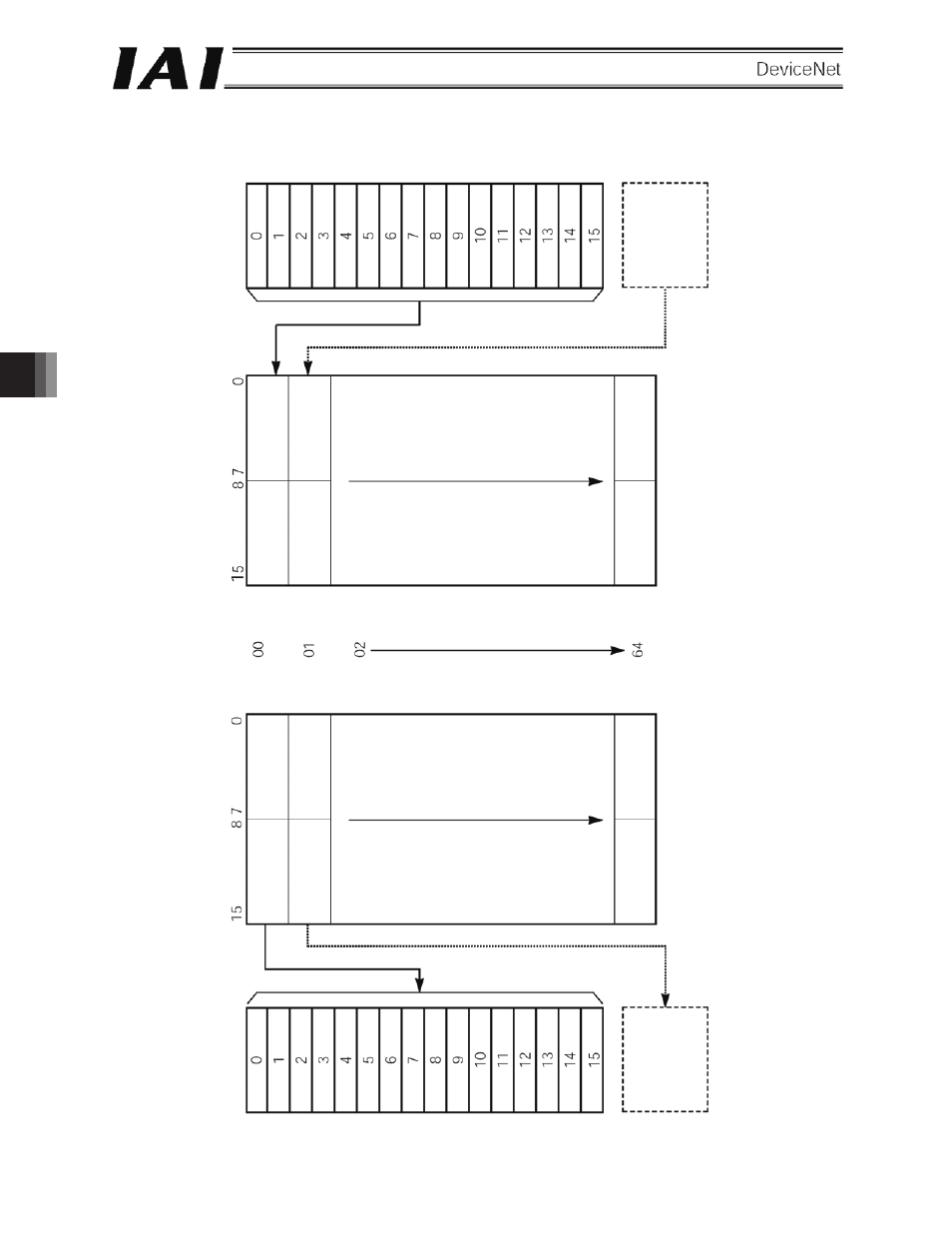

5.5 Assignment of DeviceNet Addresses

Output port No.

(bit add

re

ss)

PLC input buf

fer memo

ry

(bit position)

Nod

e add

re

ss

PLC output buffer memory

(bit position)

Input port No.

(bit add

re

ss)

•

The above figure assumes

that the node

address of the controller’s

DeviceNet board is

set to “0.”

•

I/O ports are assign

ed in u

nits of 16 poi

nts to the me

mory are

a co

rre

sp

ondi

ng to one Devi

ce

Net node add

ress.

•

I/P ports are

assigned sequentiall

y from

the youngest numbe

r, to the bits in the

buffer memory starting from the

lower bit.

6.5