2 input signals – FEC AFC1500 User Manual

Page 84

AFC1500 Multi-2 Unit Hardware Manual (Rev2.1)

PAGE 5 - 40

Chapter 5: Control Interfaces

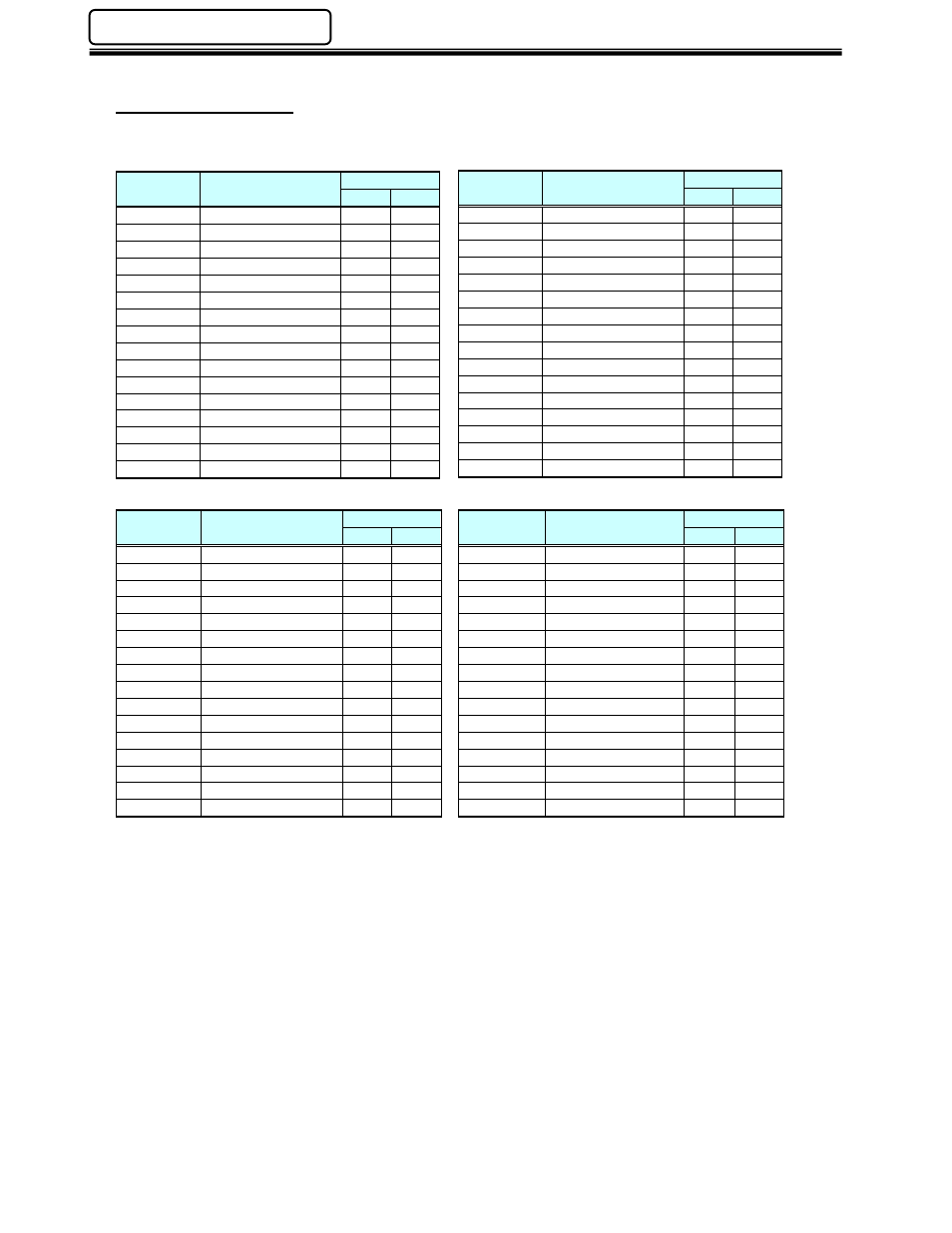

5.8.2 Input Signals

Inputs are assigned in the order as shown in the table below and cannot be changed. Bits

designated as “Unused” have no input assigned to them.

Address

Signal

FEC Multi-2

Bank

Bit

RY(n+0)0

Emergency Stop

1

RY(n+0)1

Reset

2

RY(n+0)2

Reverse

3

RY(n+0)3

Start

4

RY(n+0)4

Sequence Select 0

5

RY(n+0)5

Sequence Select 1

6

RY(n+0)6

Sequence Select 2

7

RY(n+0)7

Sequence Select 3

8

RY(n+0)8

Cycle Count Up

9

RY(n+0)9

Cycle Count Clear

10

RY(n+0)A

Self Check Disable

11

RY(n+0)B

Unused

12

RY(n+0)C

INPORT 1

13

RY(n+0)D

INPORT 2

14

RY(n+0)E

INPORT 3

15

RY(n+0)F

INPORT 4

16

Note: For signal definitions see Section 4.7.2

Address

Signal

FEC Multi-2

Bank

Bit

RY(n+1)0

BYPASS SP#1

17

RY(n+1)1

BYPASS SP#2

18

RY(n+1)2

BYPASS SP#3

19

RY(n+1)3

BYPASS SP#4

20

RY(n+1)4

BYPASS SP#5

21

RY(n+1)5

BYPASS SP#6

22

RY(n+1)6

BYPASS SP#7

23

RY(n+1)7

BYPASS SP#8

24

RY(n+1)8

BYPASS SP#9

25

RY(n+1)9

BYPASS SP#10

26

RY(n+1)A

Unused

27

RY(n+1)B

Unused

28

RY(n+1)C

Unused

29

RY(n+1)D

Unused

30

RY(n+1)E

Unused

31

RY(n+1)F

Unused

32

Address

Signal

FEC Multi-2

Bank

Bit

RY(n+2)0

BYPASS SP#11

33

RY(n+2)1

BYPASS SP#12

34

RY(n+2)2

BYPASS SP#13

35

RY(n+2)3

BYPASS SP#14

36

RY(n+2)4

BYPASS SP#15

37

RY(n+2)5

BYPASS SP#16

38

RY(n+2)6

BYPASS SP#17

39

RY(n+2)7

BYPASS SP#18

40

RY(n+2)8

BYPASS SP#19

41

RY(n+2)9

BYPASS SP#20

42

RY(n+2)A

BYPASS SP#21

43

RY(n+2)B

BYPASS SP#22

44

RY(n+2)C

BYPASS SP#23

45

RY(n+2)D

BYPASS SP#24

46

RY(n+2)E

BYPASS SP#25

47

RY(n+2)F

BYPASS SP#26

48

Address

Signal

FEC Multi-2

Bank

Bit

RY(n+3)0

BYPASS SP#27

49

RY(n+3)1

BYPASS SP#28

50

RY(n+3)2

BYPASS SP#29

51

RY(n+3)3

BYPASS SP#30

52

RY(n+3)4

BYPASS SP#31

53

RY(n+3)5

Unused

54

RY(n+3)6

Unused

55

RY(n+3)7

Unused

56

RY(n+3)8

Unused

57

RY(n+3)9

Unused

58

RY(n+3)A

Unused

59

RY(n+3)B

Unused

60

RY(n+3)C

Unused

61

RY(n+3)D

Unused

62

RY(n+3)E

Unused

63

RY(n+3)F

Unused

64