Texas Instruments MSP430x4xx User Manual

Page 71

Instruction Set

3-37

RISC 16−Bit CPU

* DEC[.W]

Decrement destination

* DEC.B

Decrement destination

Syntax

DEC

dst or

DEC.W

dst

DEC.B

dst

Operation

dst − 1 −> dst

Emulation

SUB

#1,dst

Emulation

SUB.B

#1,dst

Description

The destination operand is decremented by one. The original contents are

lost.

Status Bits

N: Set if result is negative, reset if positive

Z: Set if dst contained 1, reset otherwise

C: Reset if dst contained 0, set otherwise

V: Set if an arithmetic overflow occurs, otherwise reset.

Set if initial value of destination was 08000h, otherwise reset.

Set if initial value of destination was 080h, otherwise reset.

Mode Bits

OSCOFF, CPUOFF, and GIE are not affected.

Example

R10 is decremented by 1

DEC

R10

; Decrement R10

; Move a block of 255 bytes from memory location starting with EDE to memory location starting with

;TONI. Tables should not overlap: start of destination address TONI must not be within the range EDE

; to EDE+0FEh

;

MOV

#EDE,R6

MOV

#255,R10

L$1

MOV.B

@R6+,TONI−EDE−1(R6)

DEC

R10

JNZ

L$1

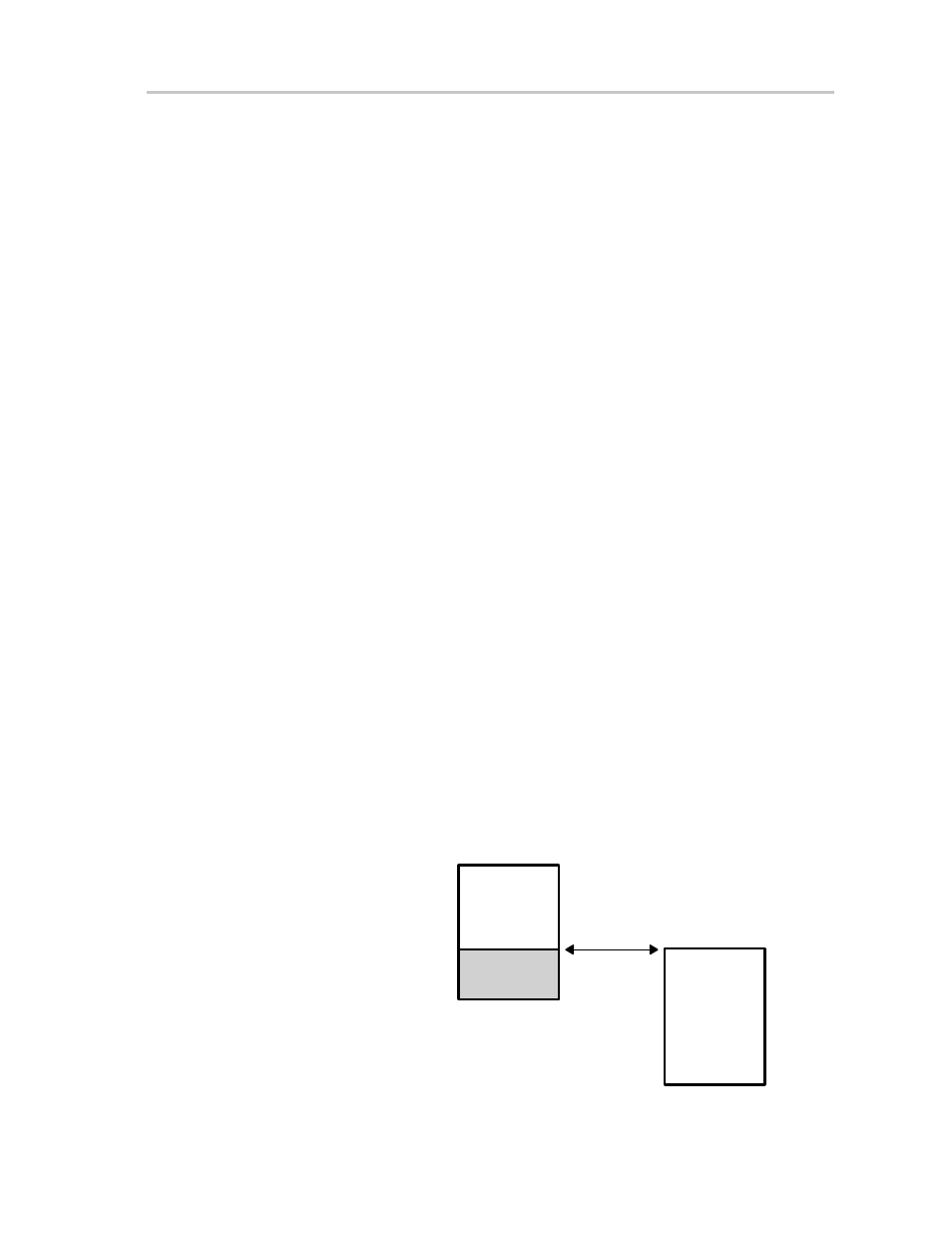

; Do not transfer tables using the routine above with the overlap shown in Figure 3−12.

Figure 3−12. Decrement Overlap

EDE

EDE+254

TONI

TONI+254