6 uart baud rate generation, Figure 14−8. bitclk baud rate timing – Texas Instruments MSP430x4xx User Manual

Page 268

USART Operation: UART Mode

14-11

USART Peripheral Interface, UART Mode

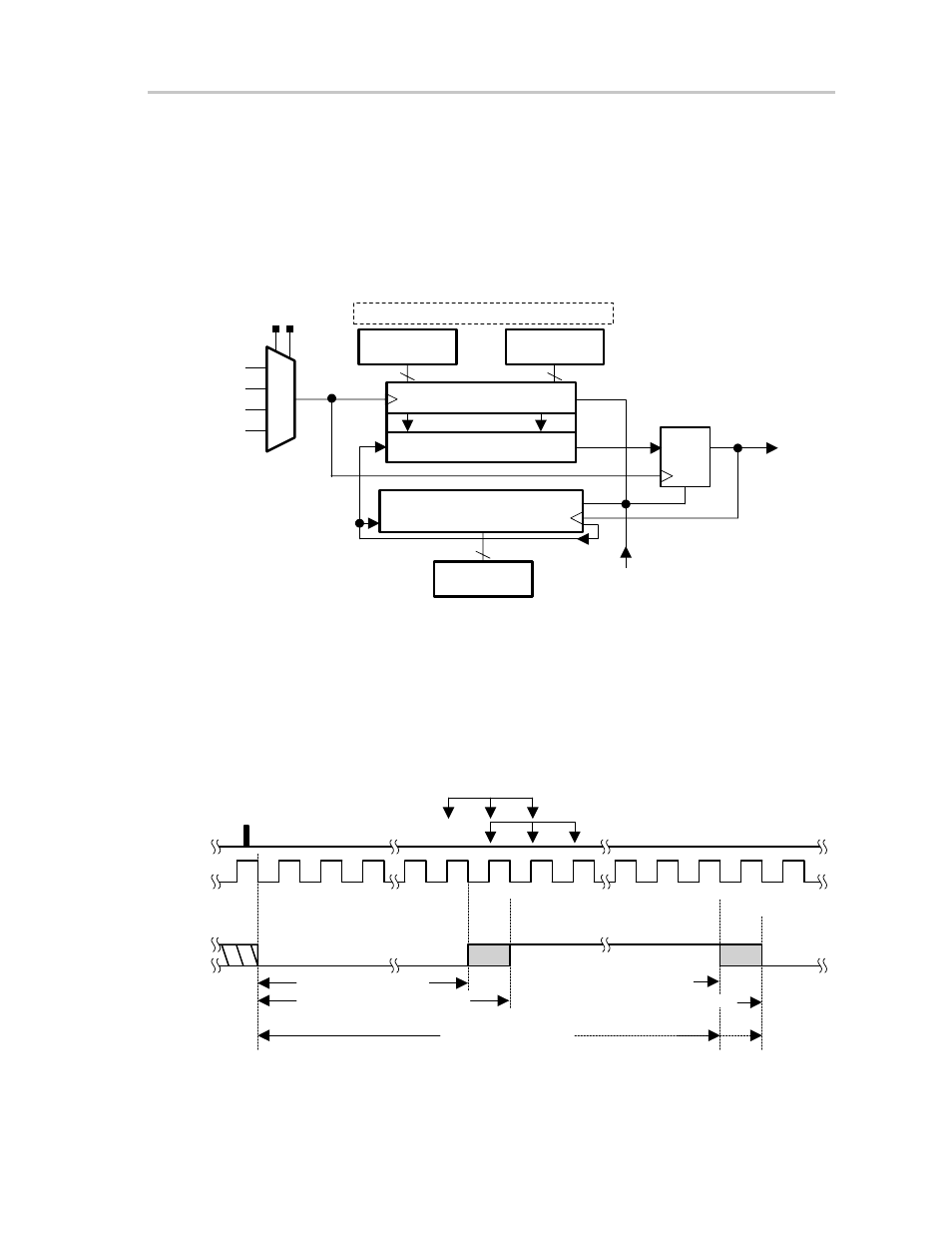

14.2.6 UART Baud Rate Generation

The USART baud rate generator is capable of producing standard baud rates

from non-standard source frequencies. The baud rate generator uses one

prescaler/divider and a modulator as shown in Figure 14−7. This combination

supports fractional divisors for baud rate generation. The maximum USART

baud rate is one-third the UART source clock frequency BRCLK.

Figure 14−7. MSP430 Baud Rate Generator

Bit Start

mX

BRCLK

8

8

UCLKI

ACLK

SMCLK

SMCLK

11

BITCLK

10

01

00

20

27

28

215

Compare (0 or 1)

Modulation Data Shift Register

(LSB first)

16−Bit Counter

Q0

............

Q15

m0

m7

...

...

8

UxBR1

UxBR0

Toggle

FF

N =

R

R

R

UxMCTL

+0 or 1

SSEL1 SSEL0

Timing for each bit is shown in Figure 14−8. For each bit received, a majority

vote is taken to determine the bit value. These samples occur at the N/2−1,

N/2, and N/2+1 BRCLK periods, where N is the number of BRCLKs per

BITCLK.

Figure 14−8. BITCLK Baud Rate Timing

N/2

Bit Start

BRCLK

Counter

BITCLK

N/2−1 N/2−2

1

N/2

N/2−1

1

N/2

N/2−1

N/2−2

0

N/2

N/2−1

1

INT(N/2) + m(= 0)

INT(N/2) + m(= 1)

1

0

N/2

Bit Period

NEVEN: INT(N/2)

NODD : INT(N/2) + R(= 1)

m: corresponding modulation bit

R: Remainder from N/2 division

Majority Vote:

(m= 0)

(m= 1)