Sifctl1, scan if control register 1 – Texas Instruments MSP430x4xx User Manual

Page 500

Scan IF Registers

24-40

Scan IF

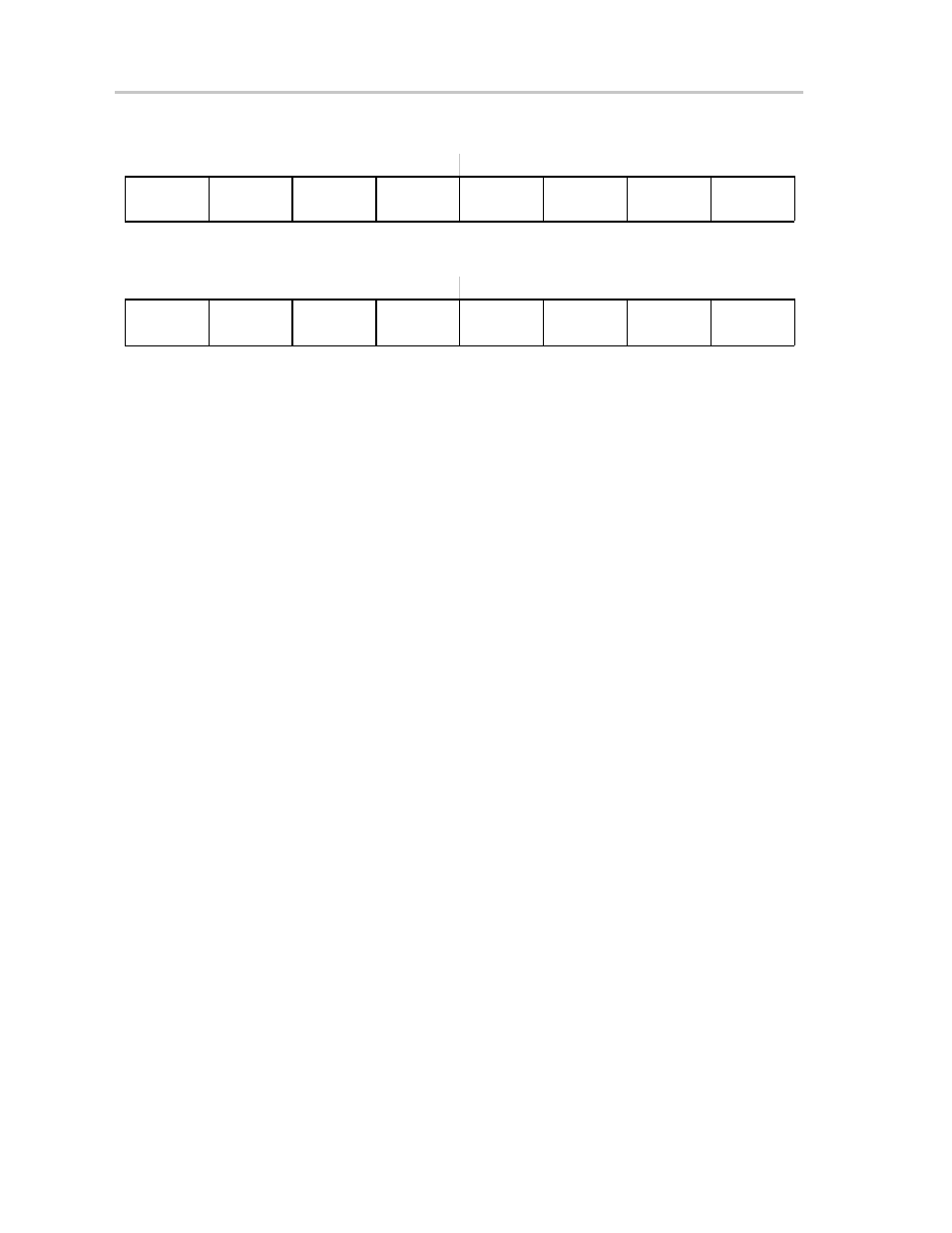

SIFCTL1, Scan IF Control Register 1

15

14

13

12

11

10

9

8

SIFIE6

SIFIE5

SIFIE4

SIFIE3

SIFIE2

SIFIE1

SIFIE0

SIFIFG6

rw−(0)

rw−(0)

rw−(0)

rw−(0)

rw−(0)

rw−(0)

rw−(0)

rw−(0)

7

6

5

4

3

2

1

0

SIFIFG5

SIFIFG4

SIFIFG3

SIFIFG2

SIFIFG1

SIFIFG0

SIFTESTD

SIFEN

rw−(0)

rw−(0)

rw−(0)

rw−(0)

rw−(0)

rw−(0)

rw−(0)

rw−(0)

SIFIEx

Bits

15-9

Interrupt Enable. These bits enable or disable the interrupt request for the

SIFIFGx bits.

0

Interrupt disabled

1

Interrupt enabled

SIFIFG6

Bit 8

SIF interrupt flag 6. This bit is set when the PSM transitions to a state with a

set Q7 bit. SIFIFG6 must be reset with software.

0

No interrupt pending

1

Interrupt pending

SIFIFG5

Bit 7

SIF interrupt flag 5. This bit is set when the PSM transitions to a state with a

set Q6 bit. SIFIFG5 must be reset with software.

0

No interrupt pending

1

Interrupt pending

SIFIFG4

Bit 6

SIF interrupt flag 4. This bit is set by the SIFCNT2 counter conditions selected

with the SIFIS2x bits. SIFIFG4 must be reset with software.

0

No interrupt pending

1

Interrupt pending

SIFIFG3

Bit 5

SIF interrupt flag 3. This bit is set by the SIFCNT1 counter conditions selected

with the SIFIS1x bits SIFIFG3 must be reset with software.

0

No interrupt pending

1

Interrupt pending

SIFIFG2

Bit 4

SIF interrupt flag 2. This bit is set at the start of a TSM sequence. SIFIFG2

must be reset with software.

0

No interrupt pending

1

Interrupt pending

SIFIFG1

Bit 3

SIF interrupt flag 1. This bit is set by the rising edge of the SIFSTOP(tsm)

signal. SIFIFG1 must be reset with software.

0

No interrupt pending

1

Interrupt pending