4 instruction cycles and lengths, Interrupt and reset cycles, Format-iii (jump) instruction cycles and lengths – Texas Instruments MSP430x4xx User Manual

Page 106

Instruction Set

3-72

RISC 16−Bit CPU

3.4.4

Instruction Cycles and Lengths

The number of CPU clock cycles required for an instruction depends on the

instruction format and the addressing modes used - not the instruction itself.

The number of clock cycles refers to the MCLK.

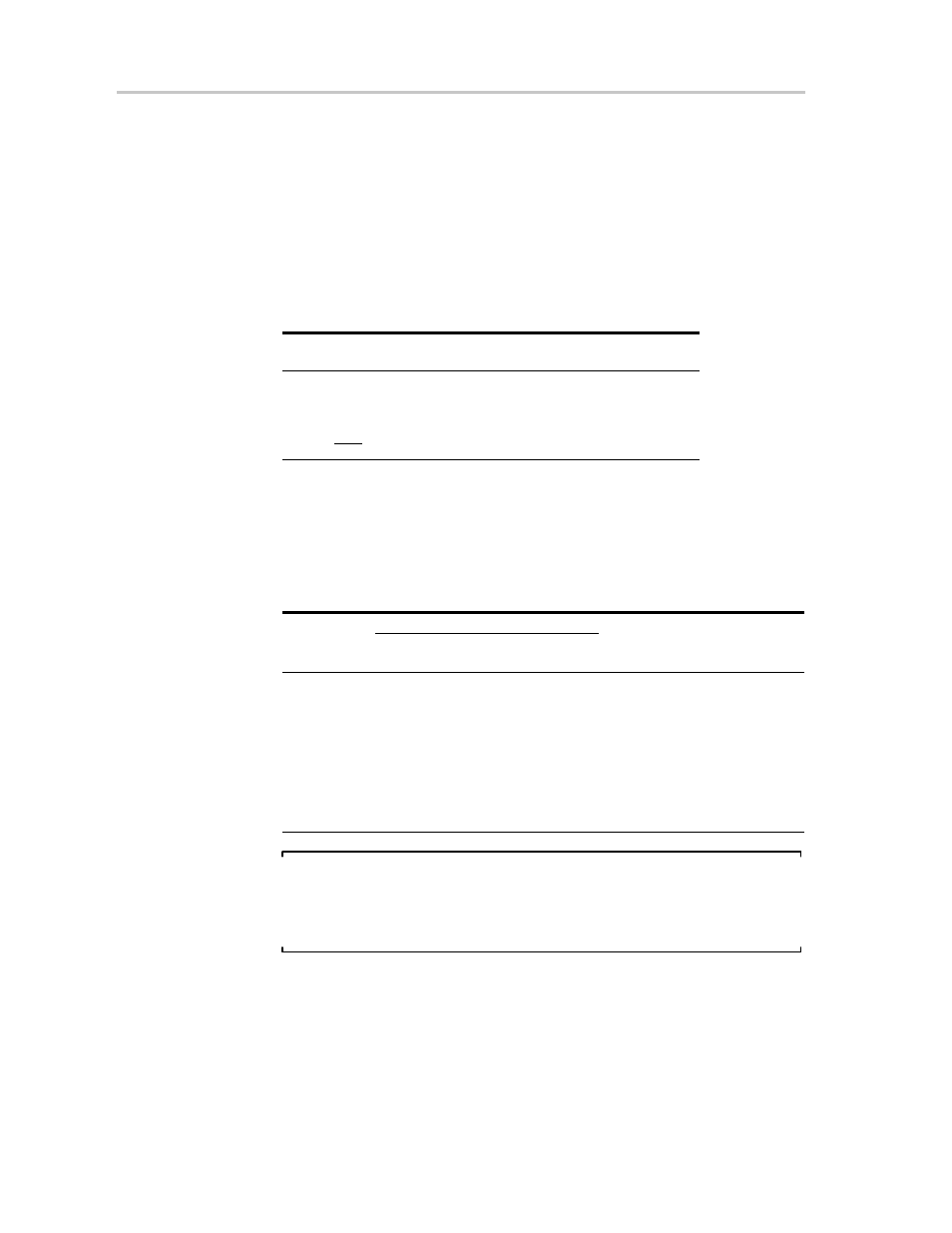

Interrupt and Reset Cycles

Table 3−14 lists the CPU cycles for interrupt overhead and reset.

Table 3−14.Interrupt and Reset Cycles

No. of

Length of

Action

No. of

Cycles

Length of

Instruction

Return from interrupt (

RETI

)

5

1

Interrupt accepted

6

−

WDT reset

4

−

Reset (RST/NMI)

4

−

Format-II (Single Operand) Instruction Cycles and Lengths

Table 3−15 lists the length and CPU cycles for all addressing modes of

format-II instructions.

Table 3−15.Format-II Instruction Cycles and Lengths

No. of Cycles

Addressing

Mode

RRA, RRC

SWPB, SXT

PUSH

CALL

Length of

Instruction

Example

Rn

1

3

4

1

SWPB R5

@Rn

3

4

4

1

RRC @R9

@Rn+

3

5

5

1

SWPB @R10+

#N

(See note)

4

5

2

CALL #0F00h

X(Rn)

4

5

5

2

CALL 2(R7)

EDE

4

5

5

2

PUSH EDE

&EDE

4

5

5

2

SXT &EDE

Note:

Instruction Format II Immediate Mode

Do not use instructions

RRA, RRC, SWPB

, and

SXT

with the immediate

mode in the destination field. Use of these in the immediate mode results in

an unpredictable program operation.

Format-III (Jump) Instruction Cycles and Lengths

All jump instructions require one code word, and take two CPU cycles to

execute, regardless of whether the jump is taken or not.