Ifg1, interrupt flag register 1 – Texas Instruments MSP430x4xx User Manual

Page 200

Watchdog Timer Registers

10-10

Watchdog Timer, Watchdog Timer+

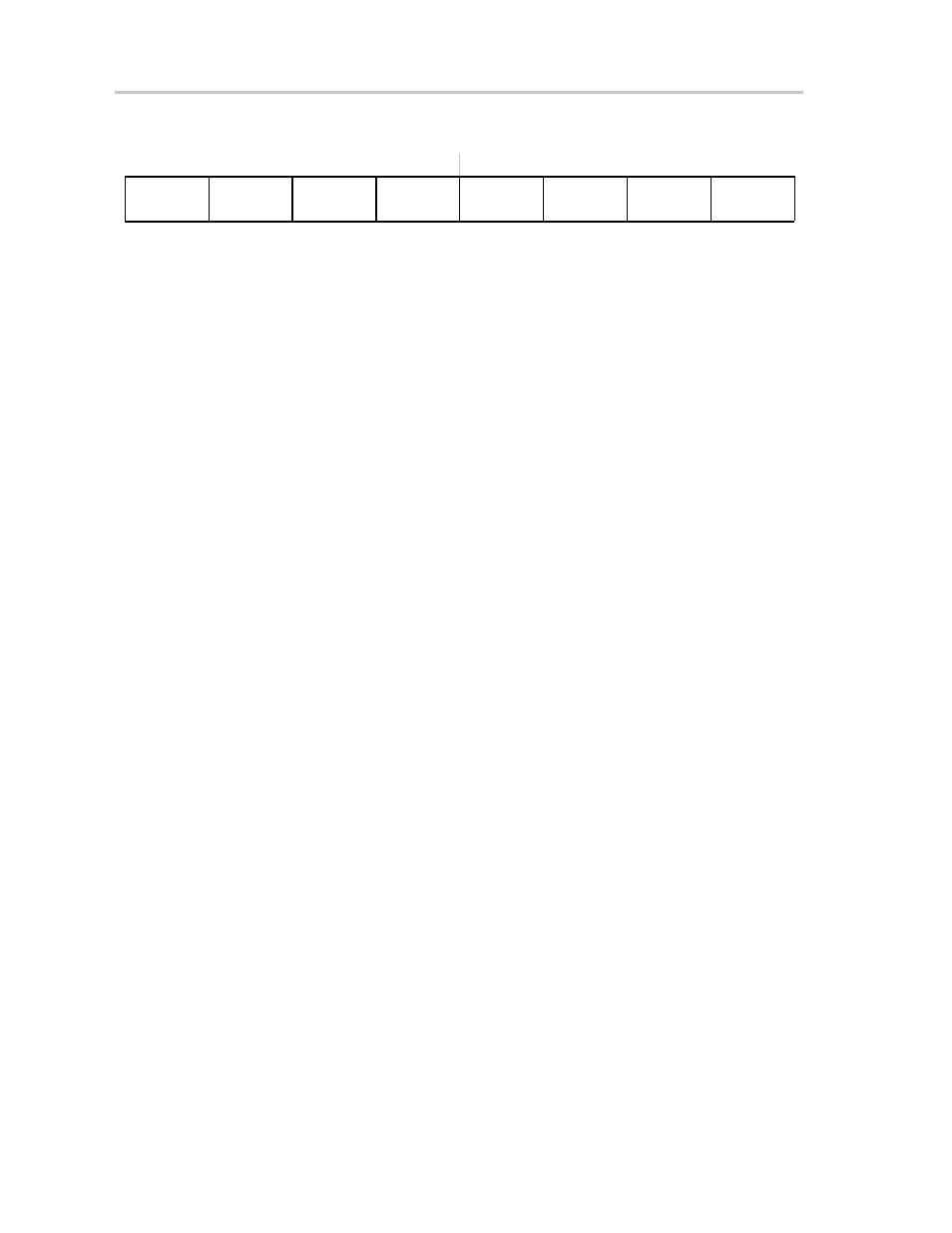

IFG1, Interrupt Flag Register 1

7

6

5

4

3

2

1

0

NMIIFG

WDTIFG

rw−(0)

rw−(0)

Bits

7-5

These bits may be used by other modules. See device-specific datasheet.

NMIIFG

Bit 4

NMI interrupt flag. NMIIFG must be reset by software. Because other bits in

IFG1 may be used for other modules, it is recommended to clear NMIIFG by

using

BIS.B

or

BIC.B

instructions, rather than

MOV.B

or

CLR.B

instructions.

0

No interrupt pending

1

Interrupt pending

Bits

3-1

These bits may be used by other modules. See device-specific datasheet.

WDTIFG

Bit 0

Watchdog timer interrupt flag. In watchdog mode, WDTIFG remains set until

reset by software. In interval mode, WDTIFG is reset automatically by

servicing the interrupt, or can be reset by software. Because other bits in IFG1

may be used for other modules, it is recommended to clear WDTIFG by using

BIS.B

or

BIC.B

instructions, rather than

MOV.B

or

CLR.B

instructions.

0

No interrupt pending

1

Interrupt pending