Uxctl, usart control register – Texas Instruments MSP430x4xx User Manual

Page 279

USART Registers: UART Mode

14-22

USART Peripheral Interface, UART Mode

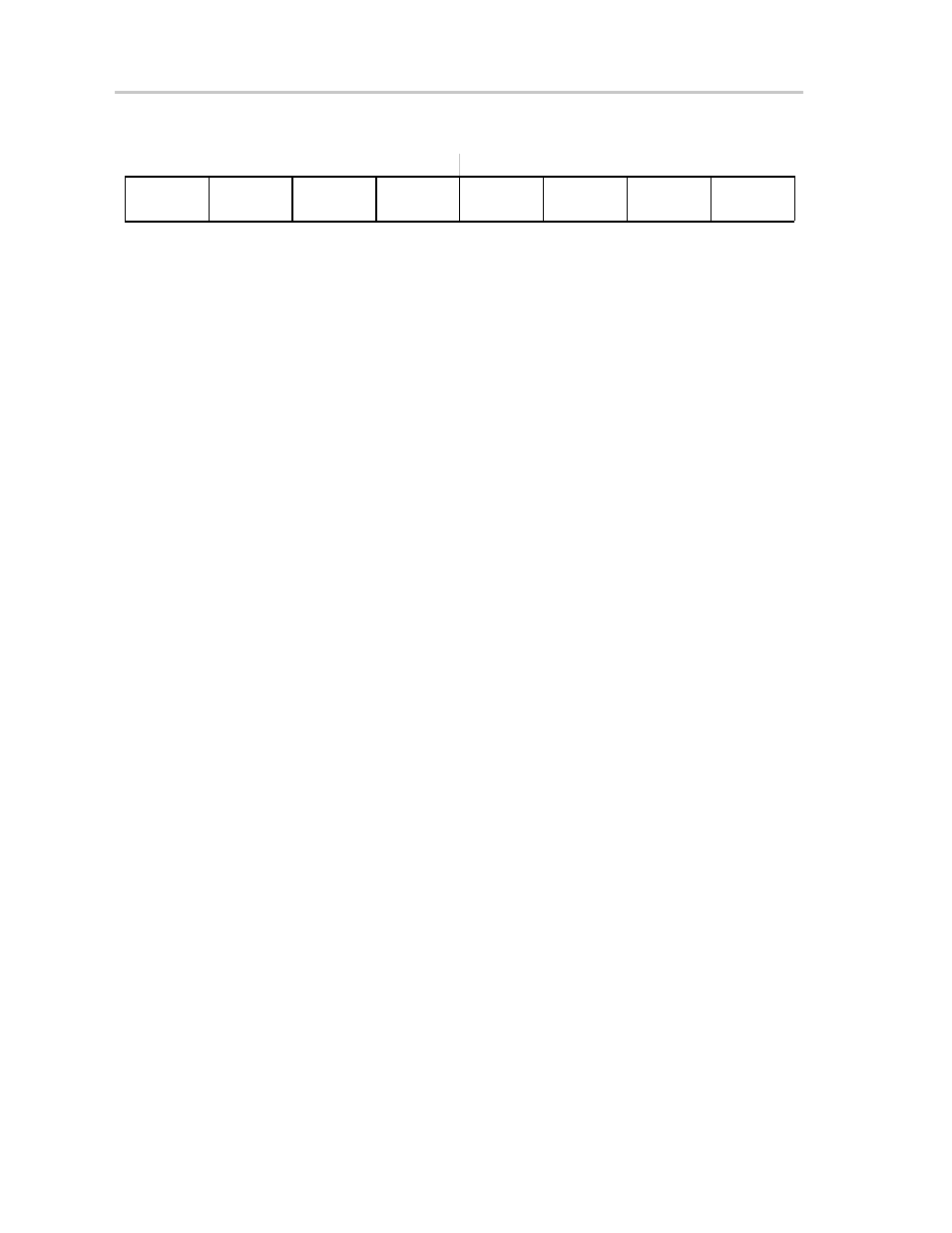

UxCTL, USART Control Register

7

6

5

4

3

2

1

0

PENA

PEV

SPB

CHAR

LISTEN

SYNC

MM

SWRST

rw−0

rw−0

rw−0

rw−0

rw−0

rw−0

rw−0

rw−1

PENA

Bit 7

Parity enable

0

Parity disabled.

1

Parity enabled. Parity bit is generated (UTXDx) and expected

(URXDx). In address-bit multiprocessor mode, the address bit is

included in the parity calculation.

PEV

Bit 6

Parity select. PEV is not used when parity is disabled.

0

Odd parity

1

Even parity

SPB

Bit 5

Stop bit select. Number of stop bits transmitted. The receiver always

checks for one stop bit.

0

One stop bit

1

Two stop bits

CHAR

Bit 4

Character length. Selects 7-bit or 8-bit character length.

0

7-bit data

1

8-bit data

LISTEN

Bit 3

Listen enable. The LISTEN bit selects loopback mode.

0

Disabled

1

Enabled. UTXDx is internally fed back to the receiver.

SYNC

Bit 2

Synchronous mode enable

0

UART mode

1

SPI Mode

MM

Bit 1

Multiprocessor mode select

0

Idle-line multiprocessor protocol

1

Address-bit multiprocessor protocol

SWRST

Bit 0

Software reset enable

0

Disabled. USART reset released for operation

1

Enabled. USART logic held in reset state