5 serial clock control, Figure 15−8. spi baud rate generator – Texas Instruments MSP430x4xx User Manual

Page 295

USART Operation: SPI Mode

15-9

USART Peripheral Interface, SPI Mode

15.2.5 Serial Clock Control

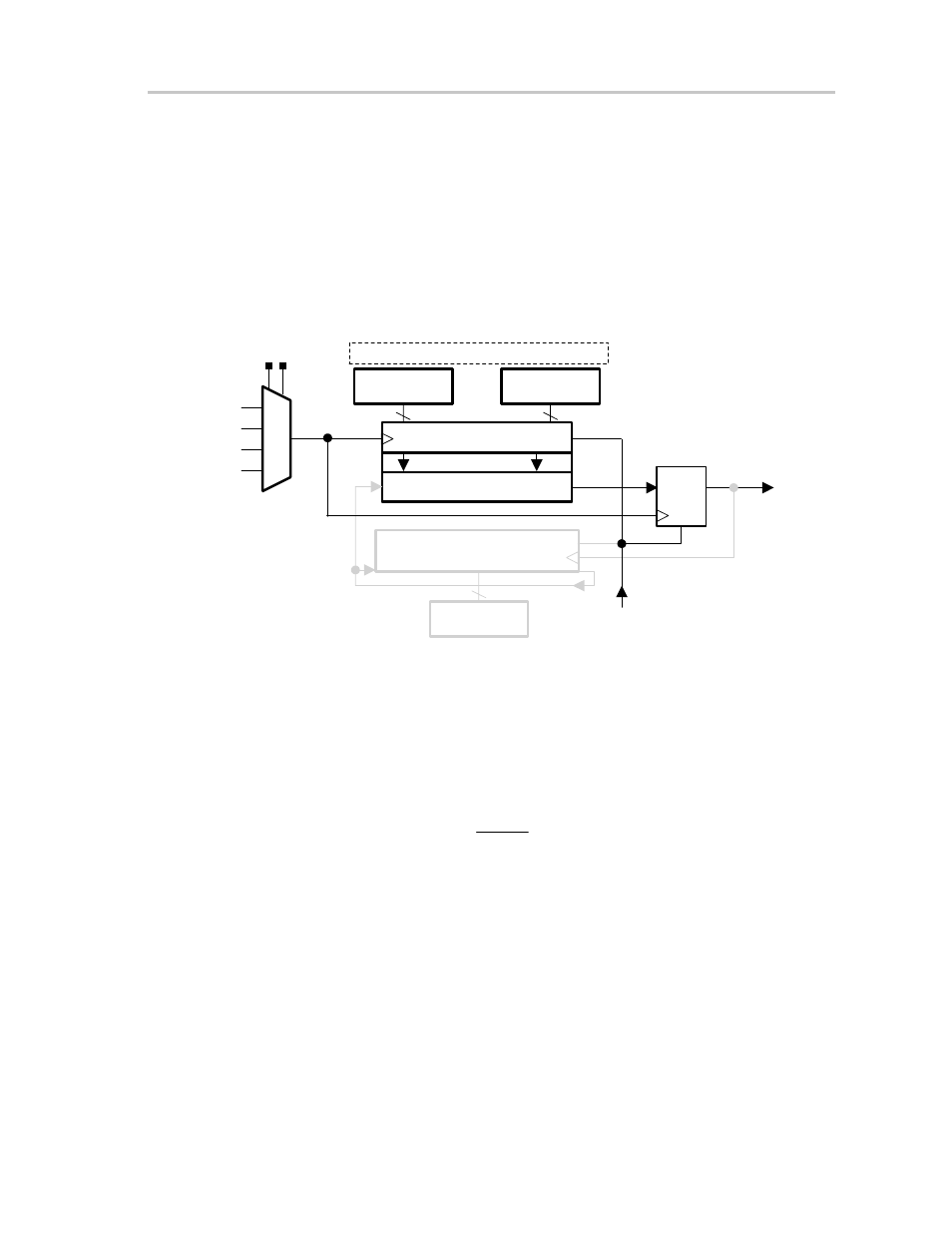

UCLK is provided by the master on the SPI bus. When MM = 1, BITCLK is

provided by the USART baud rate generator on the UCLK pin as shown in

Figure 15−8. When MM = 0, the USART clock is provided on the UCLK pin by

the master and, the baud rate generator is not used and the SSELx bits are

don’t care. The SPI receiver and transmitter operate in parallel and use the

same clock source for data transfer.

Figure 15−8. SPI Baud Rate Generator

Bit Start

mX

BRCLK

8

8

UCLKI

ACLK

SMCLK

SMCLK

11

BITCLK

10

01

00

20

27

28

215

Compare (0 or 1)

Modulation Data Shift Register

(LSB first)

16−Bit Counter

Q0

............

Q15

m0

m7

...

...

8

UxBR1

UxBR0

Toggle

FF

N =

R

R

R

UxMCTL

SSEL1 SSEL0

The 16-bit value of UxBR0+UxBR1 is the division factor of the USART clock

source, BRCLK. The maximum baud rate that can be generated in master

mode is BRCLK/2. The maximum baud rate that can be generated in slave

mode is BRCLK The modulator in the USART baud rate generator is not used

for SPI mode and is recommended to be set to 000h. The UCLK frequency is

given by:

Baud rate =

BRCLK

UxBR

with UxBR= [UxBR1, UxBR0]