Appendix d revision history – IBM uPD78082 User Manual

Page 272

249

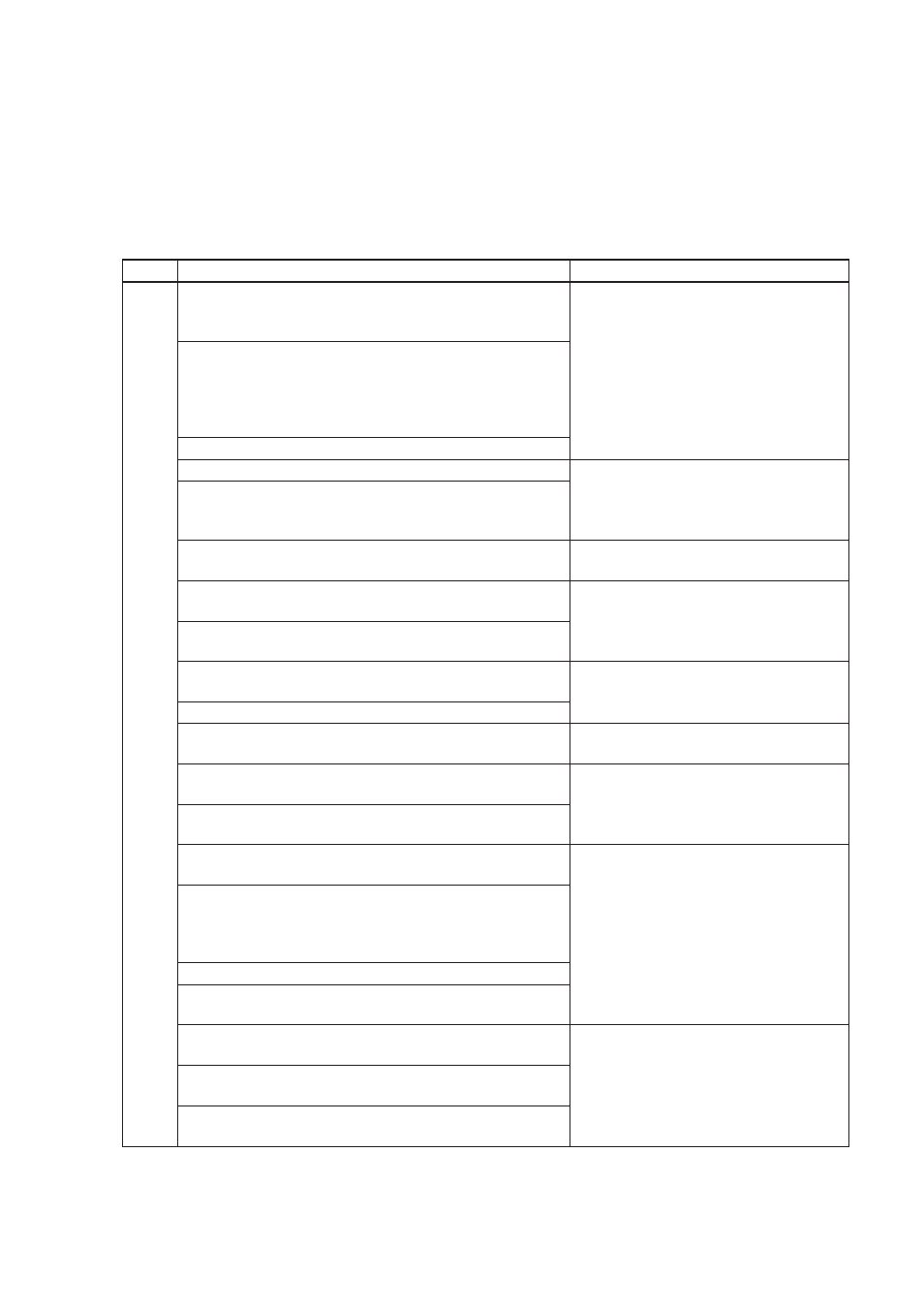

APPENDIX D REVISION HISTORY

APPENDIX D REVISION HISTORY

Major revisions by edition and revised chapters are shown below.

Edition

Major revisions from previous version

Revised Chapter

2nd

The following products have been already developed

Throughout

µ

PD78081CU-

×××

, 78081GB-

×××

-3B4, 78082CU-

×××

,

78082GB-

×××

-3B4, 78P083CU, 78P083DU, 78P083GB-3B4

The following products have been added

µ

PD78081GB-

×××

-3BS-MTX, 78082GB-

×××

-3B4-MTX,

780P083GB-3BS-MTX, 78081GB(A)-

×××

-3B4,78082GB(A)-

×××

-3B4,

78P083CU(A), 78P083GB(A)-3B4, 78P083GB(A)-3BS-MTX,

78081GB(A2)-

×××

-3B4

Power voltage changed to V

DD

= 1.8 to 5.5V.

1.6 78K/0 Series Development has been changed.

CHAPTER 1

OUTLINE

1.9 Differences between the

µ

PD78081, 78082, and 78P083,

the

µ

PD78081(A), 78082(A), and 78P083(A), and

the

µ

PD78081(A2) has been added.

Cautions regarding the use of functions in common with 2.2.5

CHAPTER 2

PIN FUNCTION

(2) (d) ASCK has been added.

Cautions concerning the Write to OSMS Command has been

CHAPTER 5

CLOCK GENERATOR

added to 5.3 (2) Oscillation mode select register (OSMS).

Cautions concerning external clock input in 5.4.1 Main system

clock oscillation has been changed.

Figure 7-3. Watchdog Timer Mode Register Format, notes and

CHAPTER 7

WATCHDOG TIMER

cautions have been added.

Description of 7.4.2 Interval timer operation has been changed.

Cautions with regard to rewriting TCL0 to other than same data

CHAPTER 8

CLOCK OUTPUT CONTROL

has been added to 8.3 (1) Timer clock select register 0 (TCL0).

CIRCUIT

The HSC bit has been added to the A/D Converter Mode

CHAPTER 10 A/D CONVERTER

Register in Figure10-1. A/D Converter Block Diagram.

10.3 (1) A/D converter mode register (ADM), 13.1.1 Standby

function, and Cautions have been added.

Figure 11-1. Serial Interface Channel 2 Block Diagram has

CHAPTER 11 SERIAL INTERFACE

been corrected.

CHANNEL 2

11.3 (4) (a), 11.4.2 (1) (d) (i) Generation of baud rate transmit/

receive clock by means of main system clock have been added.

76800 bps has been added to baud rate generated from the main

system clock.

Figure 11-10. Receive Error Timing has been corrected.

11.4.3 (c) Baud rate generator control register (BRGC) has

been added.

15.1 Memory Size Switching Register has been changed from

CHAPTER 15

µ

PD78P083

W to R/W.

Items and cautions have been added to Table 15-1. Differences

between the

µ

PD78P083 and Mask ROM Versions.

A description of the QTOP icon has been added to 15.5 Screening

of One-Time PROM Versions.