4 watchdog timer operations, 1 watchdog timer operation – IBM uPD78082 User Manual

Page 132

109

CHAPTER 7 WATCHDOG TIMER

7.4 Watchdog Timer Operations

7.4.1 Watchdog timer operation

When bit 4 (WDTM4) of the watchdog timer mode register (WDTM) is set to 1, the watchdog timer is operated

to detect any inadvertent program loop.

The watchdog timer count clock (inadvertent program loop detection time interval) can be selected with bits 0 to

2 (TCL20 to TCL22) of the timer clock select register 2 (TCL2).

Watchdog timer starts by setting bit 7 (RUN) of WDTM to 1. After the watchdog timer is started, set RUN to 1

within the set overrun detection time interval. The watchdog timer can be cleared and counting is started by setting

RUN to 1. If RUN is not set to 1 and the inadvertent program loop detection time is past, system reset or a non-maskable

interrupt request is generated according to the WDTM bit 3 (WDTM3) value.

By setting RUN to 1, the watchdog timer can be cleared.

The watchdog timer continues operating in the HALT mode but it stops in the STOP mode. Thus, set RUN to 1

before the STOP mode is set, clear the watchdog timer and then execute the STOP instruction.

Caution

The actual overrun detection time may be shorter than the set time by a maximum of

0.5 %.

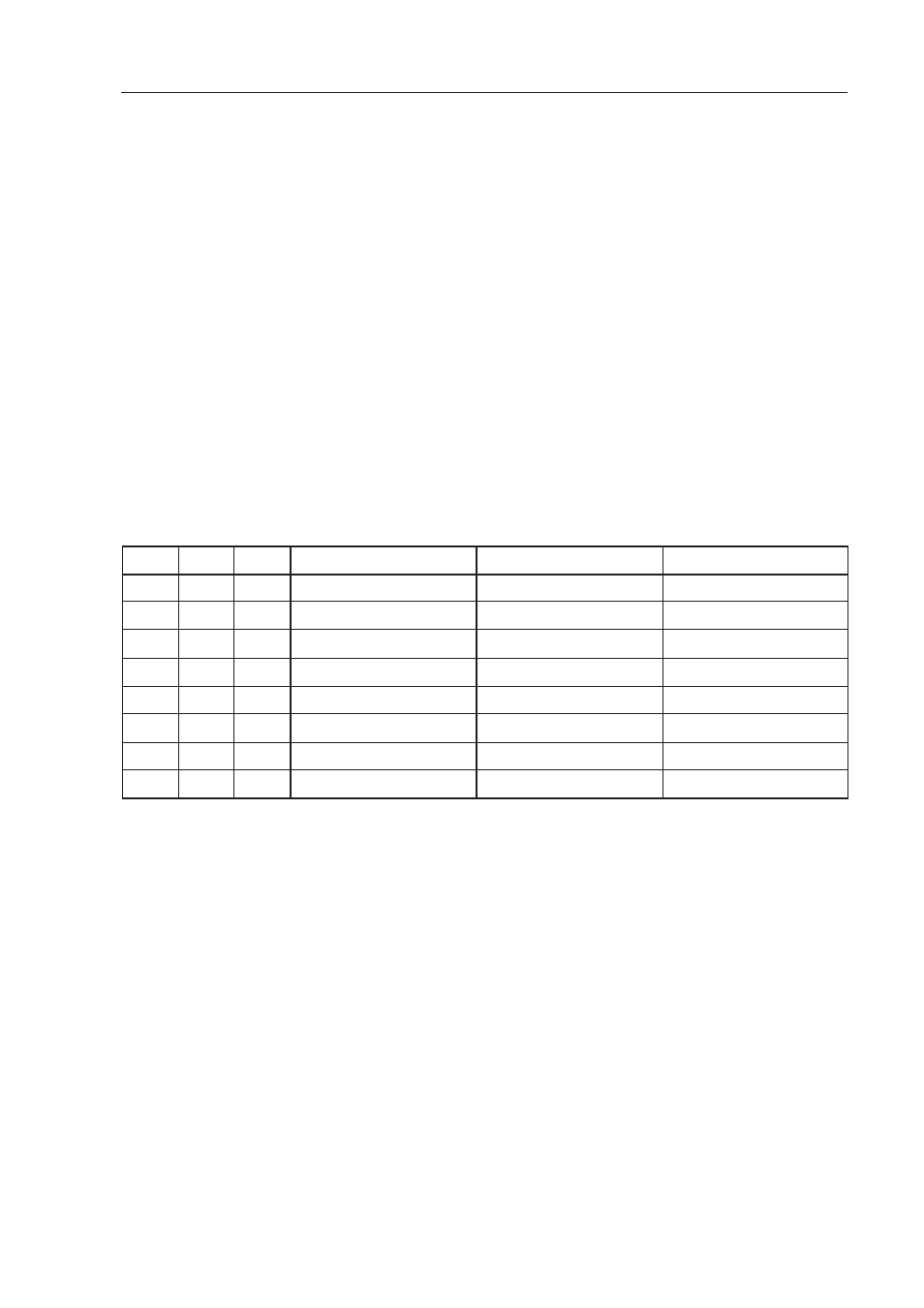

Table 7-4. Watchdog Timer Overrun Detection Time

TCL22

TCL21

TCL20

Runaway Detection Time

MCS = 1

MCS = 0

0

0

0

2

11

×

1/f

XX

2

11

×

1/f

X

(410

µ

s)

2

12

×

1/f

X

(819

µ

s)

0

0

1

2

12

×

1/f

XX

2

12

×

1/f

X

(819

µ

s)

2

13

×

1/f

X

(1.64 ms)

0

1

0

2

13

×

1/f

XX

2

13

×

1/f

X

(1.64 ms)

2

14

×

1/f

X

(3.28 ms)

0

1

1

2

14

×

1/f

XX

2

14

×

1/f

X

(3.28 ms)

2

15

×

1/f

X

(6.55 ms)

1

0

0

2

15

×

1/f

XX

2

15

×

1/f

X

(6.55 ms)

2

16

×

1/f

X

(13.1 ms)

1

0

1

2

16

×

1/f

XX

2

16

×

1/f

X

(13.1 ms)

2

17

×

1/f

X

(26.2 ms)

1

1

0

2

17

×

1/f

XX

2

17

×

1/f

X

(26.2 ms)

2

18

×

1/f

X

(52.4 ms)

1

1

1

2

19

×

1/f

XX

2

19

×

1/f

X

(104.9 ms)

2

20

×

1/f

X

(209.7 ms)

Remarks 1. f

XX

: Main system clock frequency (f

X

or f

X

/2)

2. f

X

: Main system clock oscillation frequency

3. MCS : Oscillation mode selection register (OSMS) bit 0

4. Values in parentheses when operated at f

X

= 5.0 MHz.