IBM uPD78082 User Manual

Page 115

92

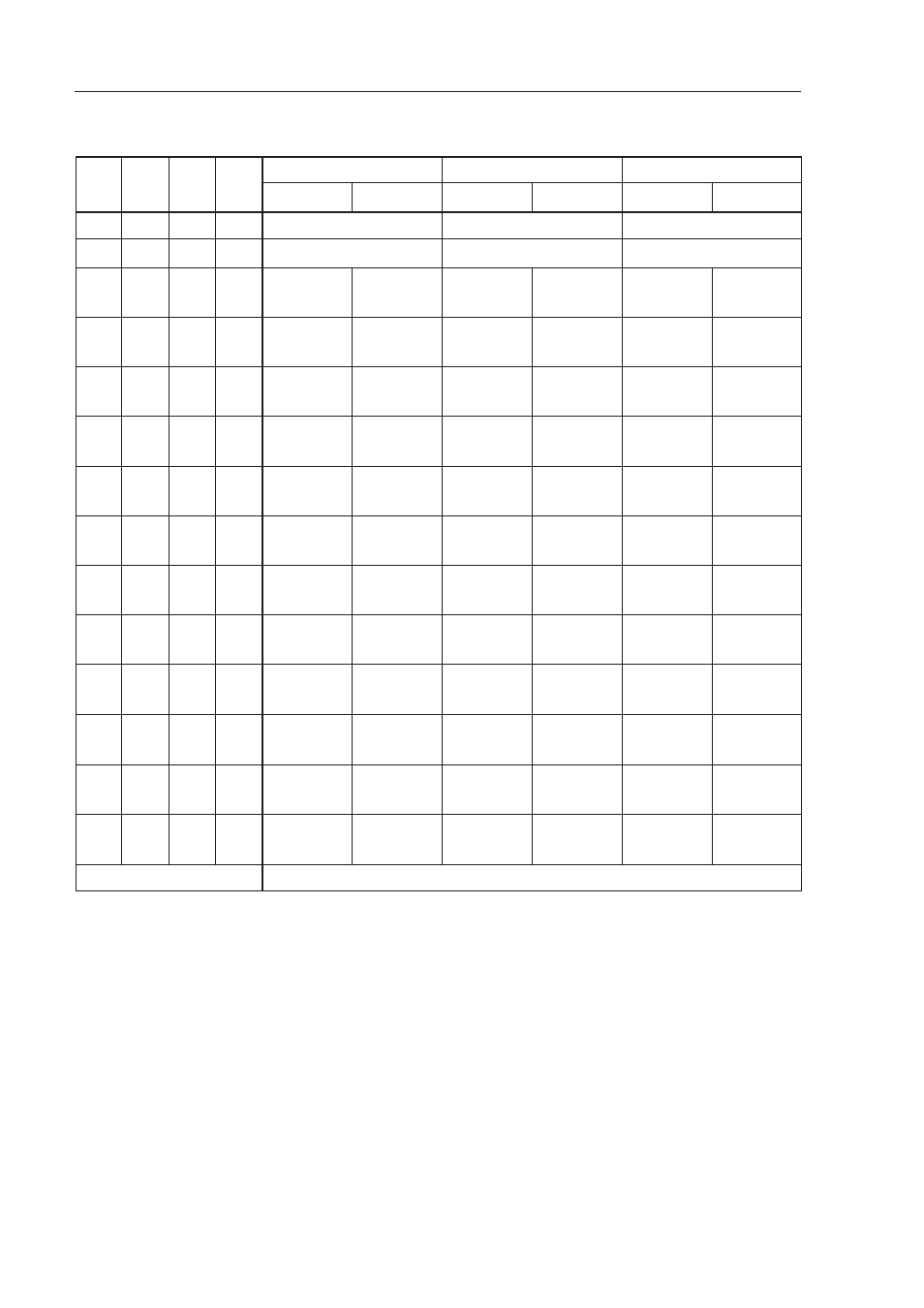

CHAPTER 6 8-BIT TIMER/EVENT COUNTERS 5 AND 6

Table 6-5. 8-Bit Timer/Event Counters 5 and 6 Interval Times

Minimum Interval Time

Maximum Interval Time

Resolution

MCS = 1

MCS = 0

MCS = 1

MCS = 0

MCS = 1

MCS = 0

0

0

0

0

TIn input cycle

2

8

×

TIn input cycle

TIn input edge cycle

0

0

0

1

TIn input cycle

2

8

×

TIn input cycle

TIn input edge cycle

Setting

1/f

X

Setting

2

8

×

1/f

X

Setting

1/f

X

prohibited

(200 ns)

prohibited

(51.2

µ

s)

prohibited

(200 ns)

1/f

X

2

×

1/f

X

2

8

×

1/f

X

2

9

×

1/f

X

1/f

X

2

×

1/f

X

(200 ns)

(400 ns)

(51.2

µ

s)

(102.4

µ

s)

(200 ns)

(400 ns)

2

×

1/f

X

2

2

×

1/f

X

2

9

×

1/f

X

2

10

×

1/f

X

2

×

1/f

X

2

2

×

1/f

X

(400 ns)

(800 ns)

(102.4

µ

s)

(204.8

µ

s)

(400 ns)

(800 ns)

2

2

×

1/f

X

2

3

×

1/f

X

2

10

×

1/f

X

2

11

×

1/f

X

2

2

×

1/f

X

2

3

×

1/f

X

(800 ns)

(1.6

µ

s)

(204.8

µ

s)

(409.6

µ

s)

(800 ns)

(1.6

µ

s)

2

3

×

1/f

X

2

4

×

1/f

X

2

11

×

1/f

X

2

12

×

1/f

X

2

3

×

1/f

X

2

4

×

1/f

X

(1.6

µ

s)

(3.2

µ

s)

(409.6

µ

s)

(819.2

µ

s)

(1.6

µ

s)

(3.2

µ

s)

2

4

×

1/f

X

2

5

×

1/f

X

2

12

×

1/f

X

2

13

×

1/f

X

2

4

×

1/f

X

2

5

×

1/f

X

(3.2

µ

s)

(6.4

µ

s)

(819.2

µ

s)

(1.64 ms)

(3.2

µ

s)

(6.4

µ

s)

2

5

×

1/f

X

2

6

×

1/f

X

2

13

×

1/f

X

2

14

×

1/f

X

2

5

×

1/f

X

2

6

×

1/f

X

(6.4

µ

s)

(12.8

µ

s)

(1.64 ms)

(3.28 ms)

(6.4

µ

s)

(12.8

µ

s)

2

6

×

1/f

X

2

7

×

1/f

X

2

14

×

1/f

X

2

15

×

1/f

X

2

6

×

1/f

X

2

7

×

1/f

X

(12.8

µ

s)

(25.6

µ

s)

(3.28 ms)

(6.55 ms)

(12.8

µ

s)

(25.6

µ

s)

2

7

×

1/f

X

2

8

×

1/f

X

2

15

×

1/f

X

2

16

×

1/f

X

2

7

×

1/f

X

2

8

×

1/f

X

(25.6

µ

s)

(51.2

µ

s)

(6.55 ms)

(13.1 ms)

(25.6

µ

s)

(51.2

µ

s)

2

8

×

1/f

X

2

9

×

1/f

X

2

16

×

1/f

X

2

17

×

1/f

X

2

8

×

1/f

X

2

9

×

1/f

X

(51.2

µ

s)

(102.4

µ

s)

(13.1 ms)

(26.2 ms)

(51.2

µ

s)

(102.4

µ

s)

2

9

×

1/f

X

2

10

×

1/f

X

2

17

×

1/f

X

2

18

×

1/f

X

2

9

×

1/f

X

2

10

×

1/f

X

(102.4

µ

s)

(204.8

µ

s)

(26.2 ms)

(52.4 ms)

(102.4

µ

s)

(204.8

µ

s)

2

11

×

1/f

X

2

12

×

1/f

X

2

19

×

1/f

X

2

20

×

1/f

X

2

11

×

1/f

X

2

12

×

1/f

X

(409.6

µ

s)

(819.2

µ

s)

(104.9 ms)

(209.7 ms)

(409.6

µ

s)

(819.2

µ

s)

Other than above

Setting prohibited

Remarks 1. f

X

: Main system clock oscillation frequency

2. MCS : Oscillation mode selection register (OSMS) bit 0

3. Values in parentheses when operated at f

X

= 5.0 MHz.

4. n = 5, 6

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

TCLn3 TCLn2 TCLn1 TCLn0