IBM uPD78082 User Manual

Page 185

162

CHAPTER 11 SERIAL INTERFACE CHANNEL 2

(3) UART mode cautions

(a) In cases where bit 7 (TXE) of the asynchronous serial interface mode register (ASIM) has been cleared

and a transmit operation has been terminated during transmission, be sure to set 1 in TXE after setting

FFH in the transmit shift register (TXS) before executing the next transmission.

(b) In cases where bit 6 (RXE) of the asynchronous serial interface mode register (ASIM) has been cleared

(0) and a receive operation terminated during reception, enable/disable will differ depending on the timing,

the condition of the receive buffer register (RXB), and generation of the reception completed interrupt

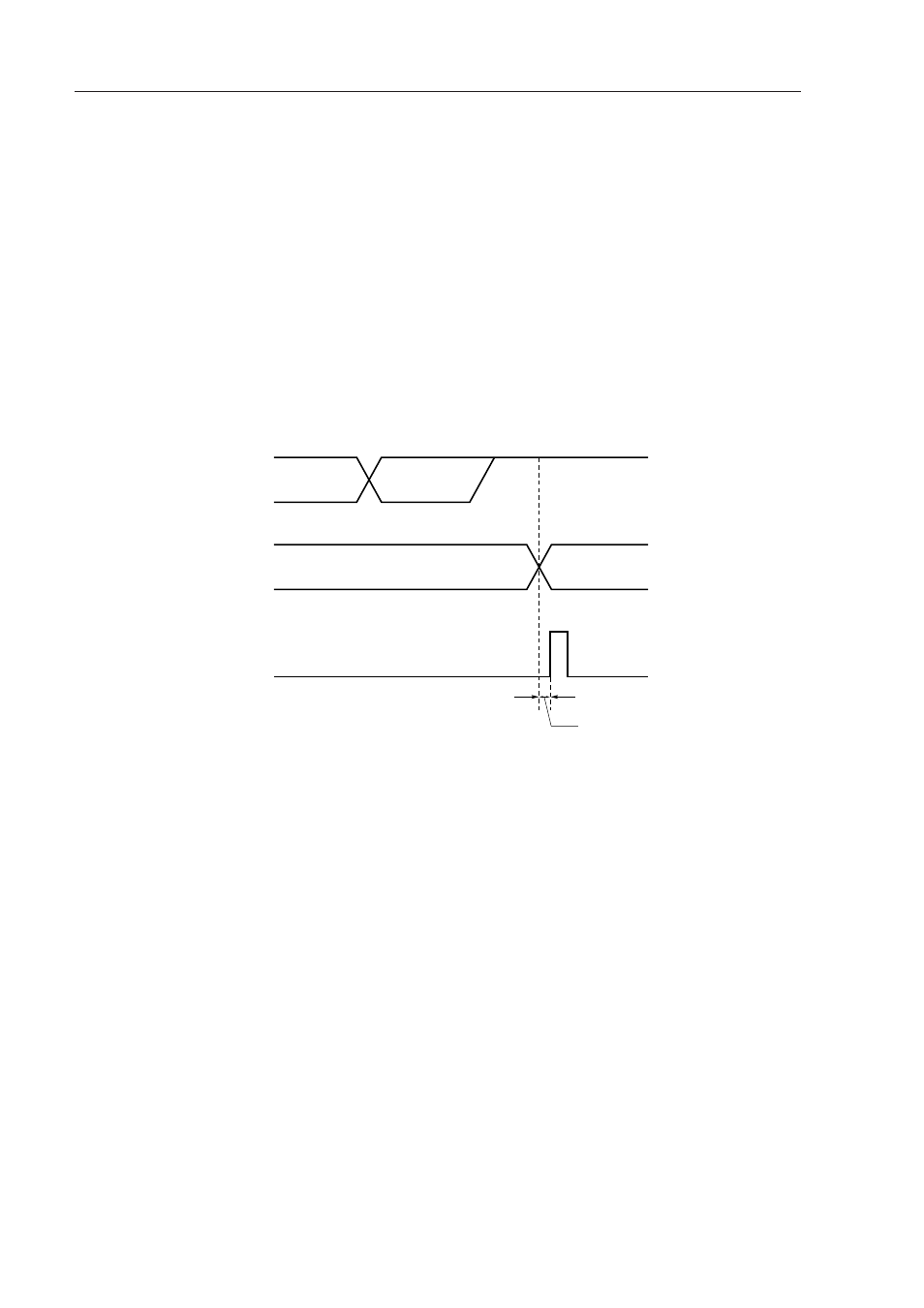

request (INTSR) . The timing is displayed in Figure 11-11.

Figure 11-11 State of the Receive Buffer Register (RXB) when Reception is Interrupted, and Generation/

Non Generation of an Interrupt Request (INTSR)

When RXE is set to 0 at a time indicated by <1>, RXB holds the previous data and does not generate INTSR.

When RXE is set to 0 at a time indicated by <2>, RXB renews the data and does not generate INTSR.

When RXE is set to 0 at a time indicated by <3>, RXB renews the data and generates INTSR.

Parity

RxD Pin

RXB

INTSR

<3>

<1>

<2>