Clock input, Clock generation – Echelon FT 3150 Smart Transceiver User Manual

Page 24

Chapter 2 - Hardware Resources

18

FT 3120 / FT 3150 Smart Transceiver Data Book

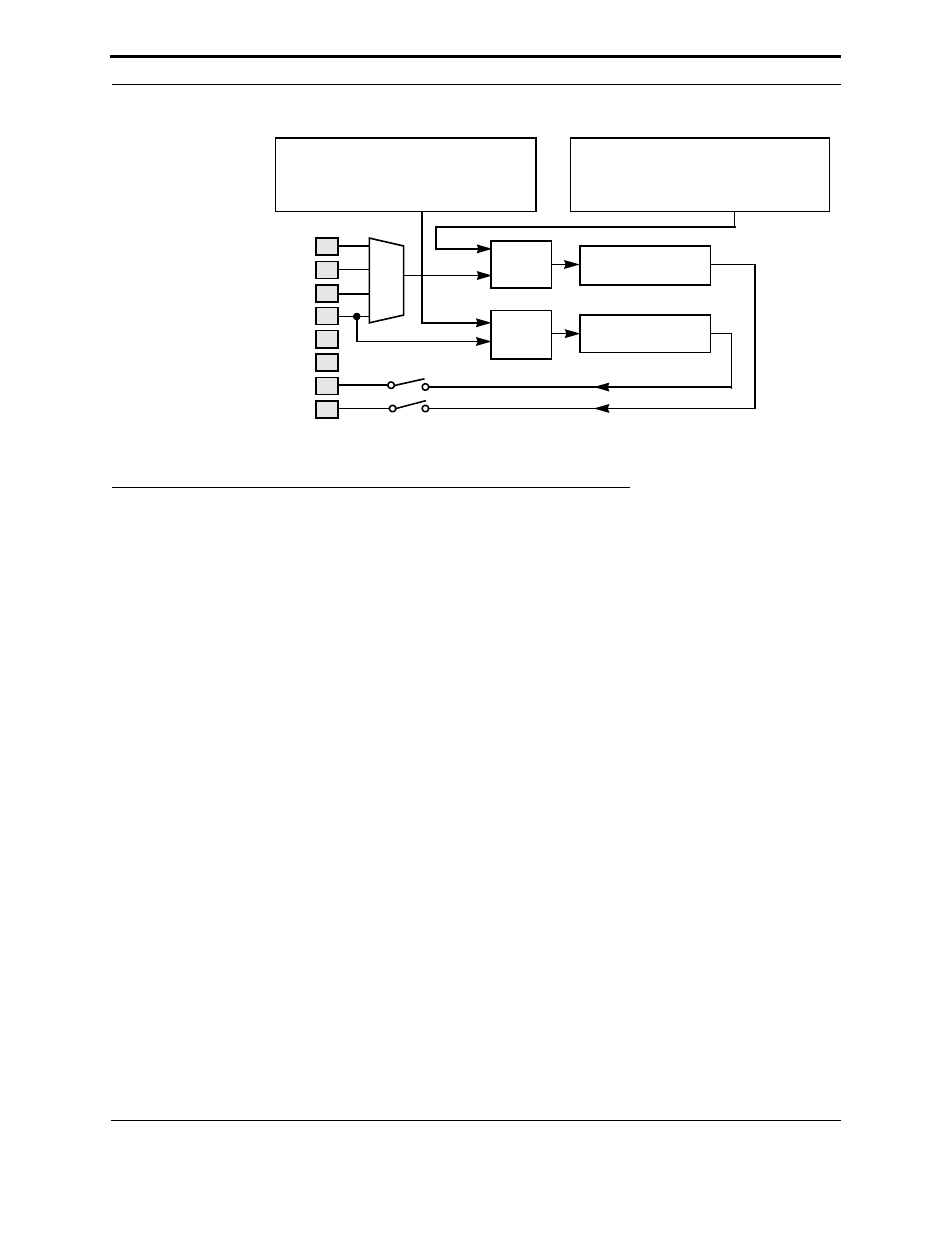

Figure 2.7 Timer/Counter Circuits

Clock Input

The FT Smart Transceivers operate with an input clock of 5, 10, or 20MHz. The FT 3120 Smart Transceiver also

supports 40MHz operation. Developers who are using the LonBuilder 3.0.1 or NodeBuilder 1.5 tools and are

upgrading to a clock speed higher than 10MHz should refer to the readme.txt file included in the latest Service Pack

for the LonBuilder 3.01, or for NodeBuilder 1.5 tools for an in-depth discussion about the software considerations on

each platform. The NodeBuilder 3.2 (or later) development tool contains built-in support for these higher clock

speeds.

Clock Generation

The FT Smart Transceiver divides the input clock by a factor of two to provide a symmetrical on-chip system clock.

The input clock may be generated either by an external free-running oscillator or by the on-chip oscillator in the

Smart Transceiver using an external parallel-mode resonant crystal.

The accuracy of the input clock frequency of the FT Smart Transceiver must be ±200ppm or better; this requirement

can be met with a suitable crystal, but cannot be met with a ceramic resonator.

The FT Smart Transceiver includes an oscillator that may be used to generate an input clock using an external crystal.

For 5 MHz, 10MHz, and 20MHz, either an external clock source or the on-chip crystal oscillator may be used. For

40MHz operation of an FT 3120 Smart Transceiver, an external oscillator must be used.

When an externally generated clock is used to drive the CLK1 CMOS input pin of the FT Smart Transceiver, CLK2

must be left unconnected or used to drive no more than one external CMOS load. The accuracy of the clock

frequency must be ± 0.02% (200 ppm) or better, to ensure that devices may correctly synchronize their bit clocks.

Figure 2.8 shows the crystal oscillator circuit. Use the load capacitance and resistor values recommended by the

manufacturer of the crystal for this circuit. A 60/40 duty cycle or better is required when using an external oscillator

as shown in Figure 2.9. An external oscillator must provide CMOS voltage levels to the CLK1 pin.

System Clock Divide

Chain

Timer/Counter 2

Timer/Counter 1

IO0

IO1

IO2

IO3

IO4

IO5

IO6

IO7

MUX

System Clock Divide

Chain

Control

Logic

Control

Logic