Overview, Neuron processor architecture, Overview neuron processor architecture – Echelon FT 3150 Smart Transceiver User Manual

Page 14

Chapter 2 - Hardware Resources

8

FT 3120 / FT 3150 Smart Transceiver Data Book

Overview

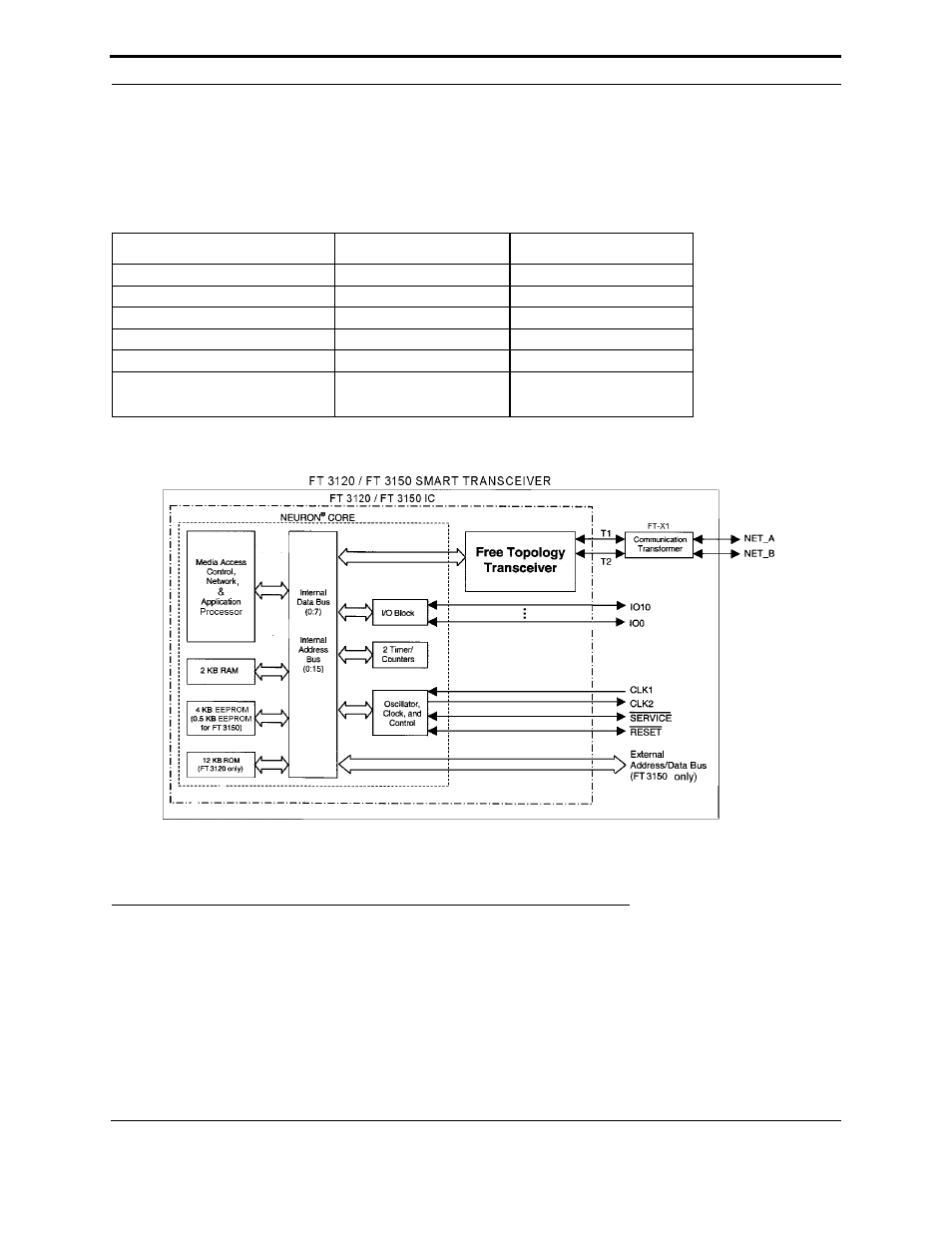

The FT 3150 Smart Transceiver supports external memory for more complex applications, while the FT 3120 Smart

Transceiver is a complete system on a chip. The major hardware blocks of both processors are the same, except where

noted in the table and figure below.

Table 2.1 Comparison of FT Smart Transceivers

Figure 2.1 FT Smart Transceiver Block Diagram

Neuron Processor Architecture

The Neuron core is composed of three processors. These processors are assigned to the following functions by the

Neuron firmware.

Processor 1 is the MAC layer processor that handles layers 1 and 2 of the 7-layer LonTalk

®

protocol stack. This

includes driving the communications subsystem hardware and executing the media access control algorithm.

Processor 1 communicates with Processor 2 using network buffers located in shared RAM memory.

Characteristic

FT 3150 Smart Transceiver FT 3120 Smart Transceiver

RAM Bytes

2,048

2,048

ROM Bytes

—

12,288

EEPROM Bytes

512

4,096

16-Bit Timer/Counters

2

2

External Memory Interface

Yes

No

Package

64 pin TQFP

32 pin SOIC

44 pin TQFP