Compact class lsw b, Watlow ez-zone, Rma module – Watlow EZ-ZONE RMA Modul User Manual

Page 73: Chapter 8 appendix

Watlow EZ-ZONE

®

RMA Module

•

70

•

Chapter 8 Appendix

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

spare

Limit

clear

Clear

latched

error

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

spare

Limit

clear

spare

Limit

clear

spare

Limit

clear

spare

Limit

clear

spare

Limit

clear

spare

Limit

clear

spare

Limit

clear

spare

Limit

clear

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Alarm

clear

Alarm

silence

Alarm

clear

Alarm

silence

Alarm

clear

Alarm

silence

Alarm

clear

Alarm

silence

Alarm

clear

Alarm

silence

Alarm

clear

Alarm

silence

Alarm

clear

Alarm

silence

Alarm

clear

Alarm

silence

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Alarm

silence

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

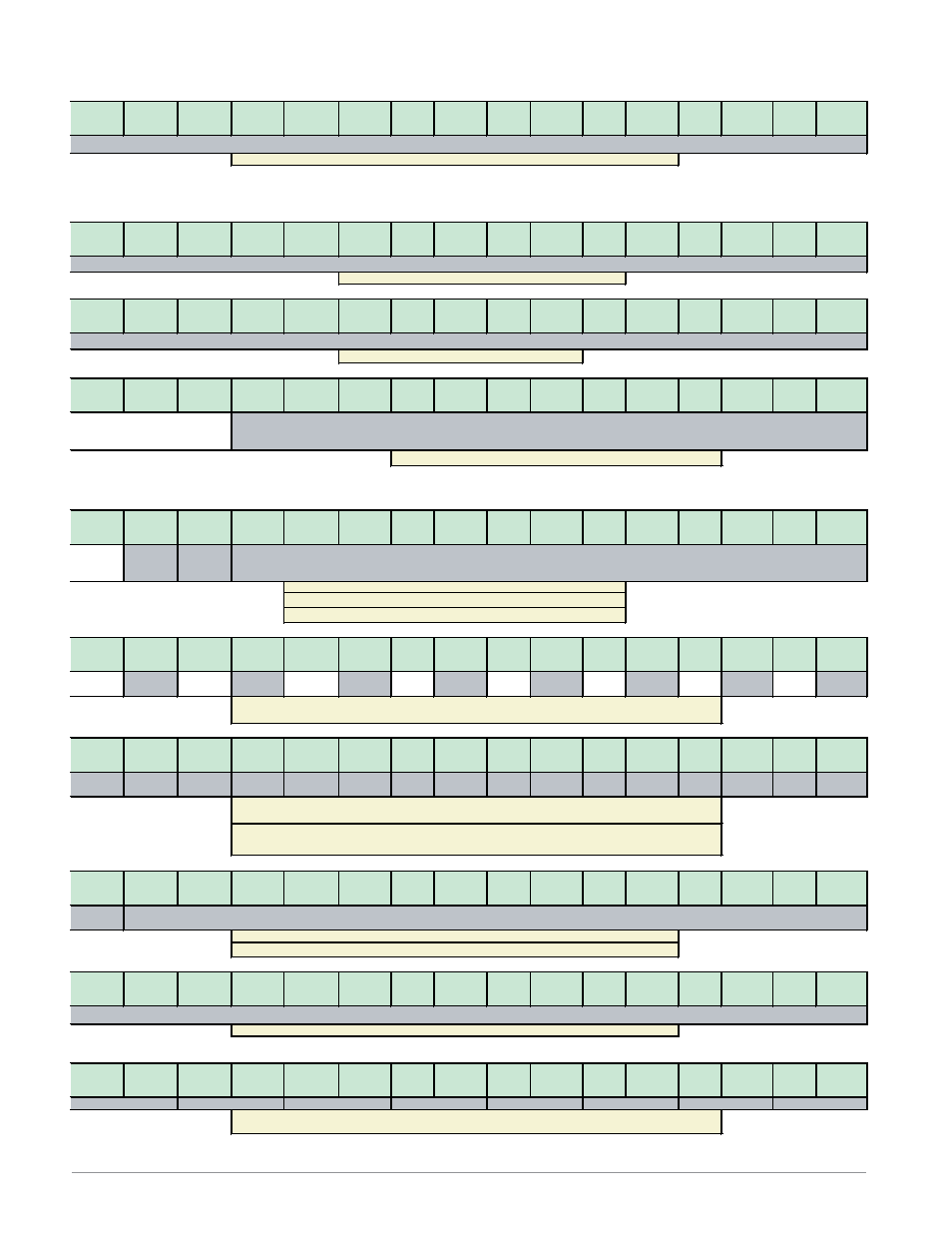

Bits 0 to 12, Signed 13 bits whole (-4096 to 4095)

Bits 0 to 12, Signed 13 bits whole (-4096 to 4095)

Bits 13, Clear Latched Input Error (0 = Ignore, 1 = Clear)

Bits 14, Clear Latched Error (0 = Ignore, 1 = Clear)

Bits 0 to 15, Signed 16 bits with implied tenths precision (-3276.8 to 3276.7)

Bits 0 to 15, Unsigned 16 bits whole (0 to 6553.5)

Bits 0, 2, 4, 6, 8, 10, 12, and 14, Limit Clear for instance i to instance i + 15 respectively (0 = Ignore, 1

= Clear)

Bits 0, 2, 4, 6, 8, 10, 12, and 14, Alar m Silence for instance i to instance i + 15 respectively (0 = Ignore,

1 = Clear)

Bits 1, 3, 5, 7, 9, 11, 13 and 15, Alar m Clear for instance i to instance i + 15 respectively (0 = Ignore, 1

= Silence)

Bits 0 to 15 and 16 to 31, Signed 16 bits with implied tenths precision (-3276.8 to 3276.7)

Digital State

Bits 0 to 14, Signed 15 bits with implied tenths precision (-1638.4 to 1638.3)

Bits 0 to 15, Signed 16 bits with implied tenths precision (-3276.8 to 3276.7)

Integral Time (instance i)

Derivative Time (instance i)

Analog Value

Closed Loop Set Point (instance i)

Digital State

Digital State

Digital State

Digital State

Digital State

Digital State

Digital State

Alarm Set Point Low (instance i)

Bits 0 to 15, Unsigned 16 bits whole (0 to 6553.5)

Limit Set Point Low (instance i)

spare

Limit Set Point High (instance i)

Bit 15, Alarm Silence (0 = Ignore, 1 = Silence)

Bits 0 to 15, This member has paired bits which represent the digital state of up to 8 Variables

instance i to instance i + 15 respectively (00 = Off, 01 = On)

Compact Class LSW B