Rainbow Electronics DS2154 User Manual

Page 18

DS2154

031197 18/69

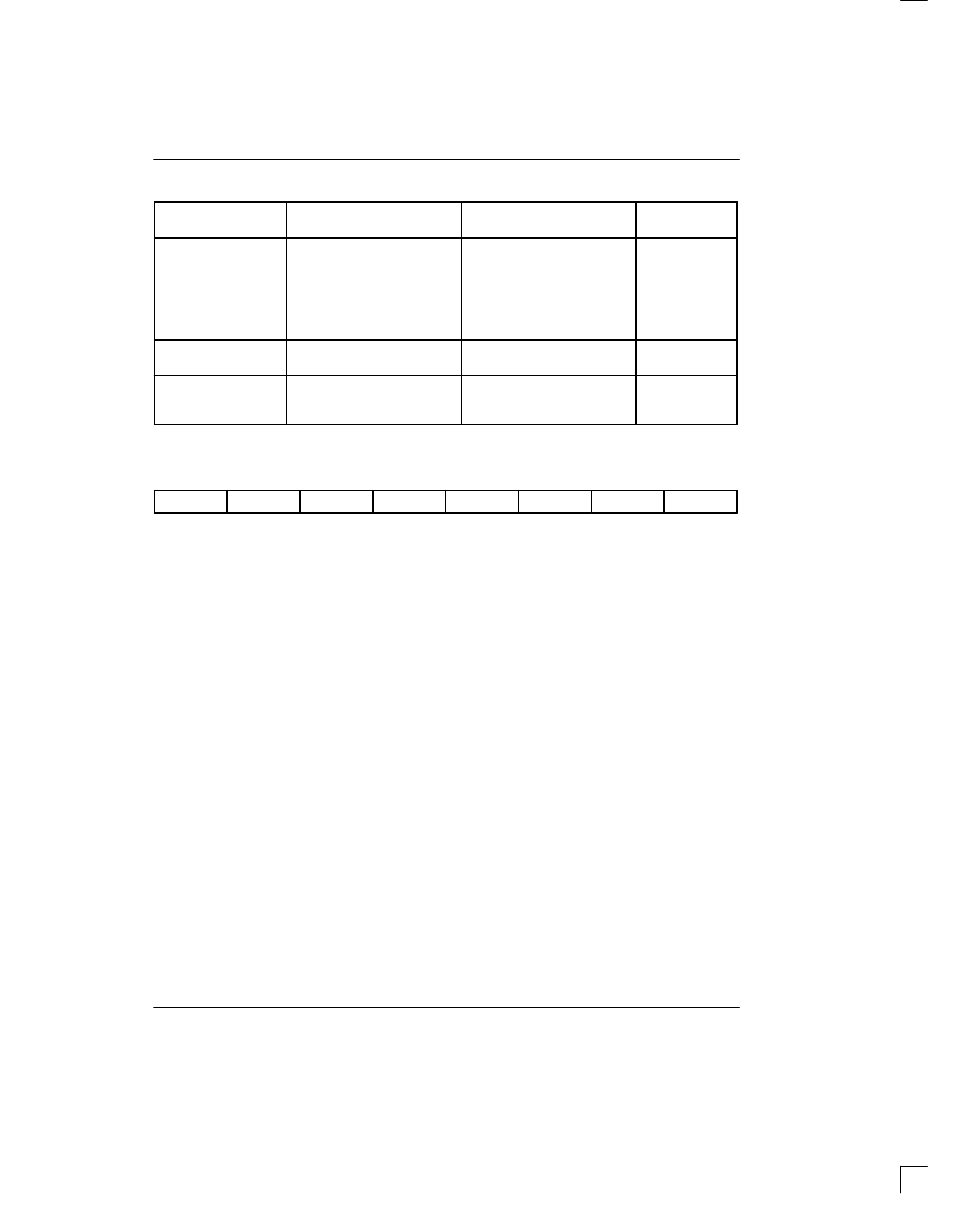

SYNC/RESYNC CRITERIA Table 3–1

FRAME OR MULTI-

FRAME LEVEL

SYNC CRITERIA

RESYNC CRITERIA

ITU SPEC.

FAS

FAS present in frame N and

N + 2, and FAS not present in

frame N + 1

Three consecutive incorrect

FAS received

Alternate (RCR1.2=1) the

above criteria is met or three

consecutive incorrect bit 2 of

non–FAS received

G.706

4.1.1

4.1.2

CRC4

Two valid MF alignment words

found within 8 ms

915 or more CRC4 code words

out of 1000 received in error

G.706

4.2 and 4.3.2

CAS

Valid MF alignment word found

and previous timeslot 16 con-

tains code other than all zeros

Two consecutive MF alignment

words received in error

G.732

5.2

RCR2: RECEIVE CONTROL REGISTER 2 (Address=11 Hex)

(MSB)

(LSB)

Sa8S

Sa7S

Sa6S

Sa5S

Sa4S

RBCS

RESE

–

SYMBOL

POSITION

NAME AND DESCRIPTION

Sa8S

RCR2.7

Sa8 Bit Select. Set to one to have RLCLK pulse at the Sa8 bit position; set

to zero to force RLCLK low during Sa8 bit position. See Section 13 for tim-

ing details.

Sa7S

RCR2.6

Sa7 Bit Select. Set to one to have RLCLK pulse at the Sa7 bit position; set

to zero to force RLCLK low during Sa7 bit position. See Section 13 for tim-

ing details.

Sa6S

RCR2.5

Sa6 Bit Select. Set to one to have RLCLK pulse at the Sa6 bit position; set

to zero to force RLCLK low during Sa6 bit position. See Section 13 for tim-

ing details.

Sa5S

RCR2.4

Sa5 Bit Select. Set to one to have RLCLK pulse at the Sa5 bit position; set

to zero to force RLCLK low during Sa5 bit position. See Section 13 for tim-

ing details.

Sa4S

RCR2.3

Sa4 Bit Select. Set to one to have RLCLK pulse at the Sa4 bit position; set

to zero to force RLCLK low during Sa4 bit position. See Section 13 for tim-

ing details.

RBCS

RCR2.2

Receive Side Backplane Clock Select.

0=if RSYSCLK is 1.544 MHz

1=if RSYSCLK is 2.048 MHz

RESE

RCR2.1

Receive Side Elastic Store Enable.

0=elastic store is bypassed

1=elastic store is enabled

–

RCR2.0

Not Assigned. Should be set to zero when written.