Aic: advanced interrupt controller – Rainbow Electronics AT75C310 User Manual

Page 29

AT75C310

29

AIC: Advanced Interrupt Controller

The AT75C310 has an eight-level priority, individually

maskable interrupt controller. This feature substantially

reduces the software and real-time overhead in handling

internal and external interrupts.

The interrupt controller is connected to the NFIQ (fast inter-

rupt request) and the NIRQ (standard interrupt request)

inputs of the ARM7TDMI processor. The processor’s NFIQ

line can only be asserted by the external fast interrupt

request input FIQ. The NIRQ line can be asserted by the

interrupts generated by the on-chip peripherals and the

external interrupt request lines IRQ0 and FIQ.

The eight-level priority encoder allows the customer to

define the priority between the different NIRQ interrupt

sources.

Internal sources are programmed to be level-sensitive or

edge-triggered. External sources can be programmed to be

positive- or negative-edge triggered or high- or low-level

sensitive.

The interrupt sources are listed in Table 11 and the AIC

programmable registers in Table 12.

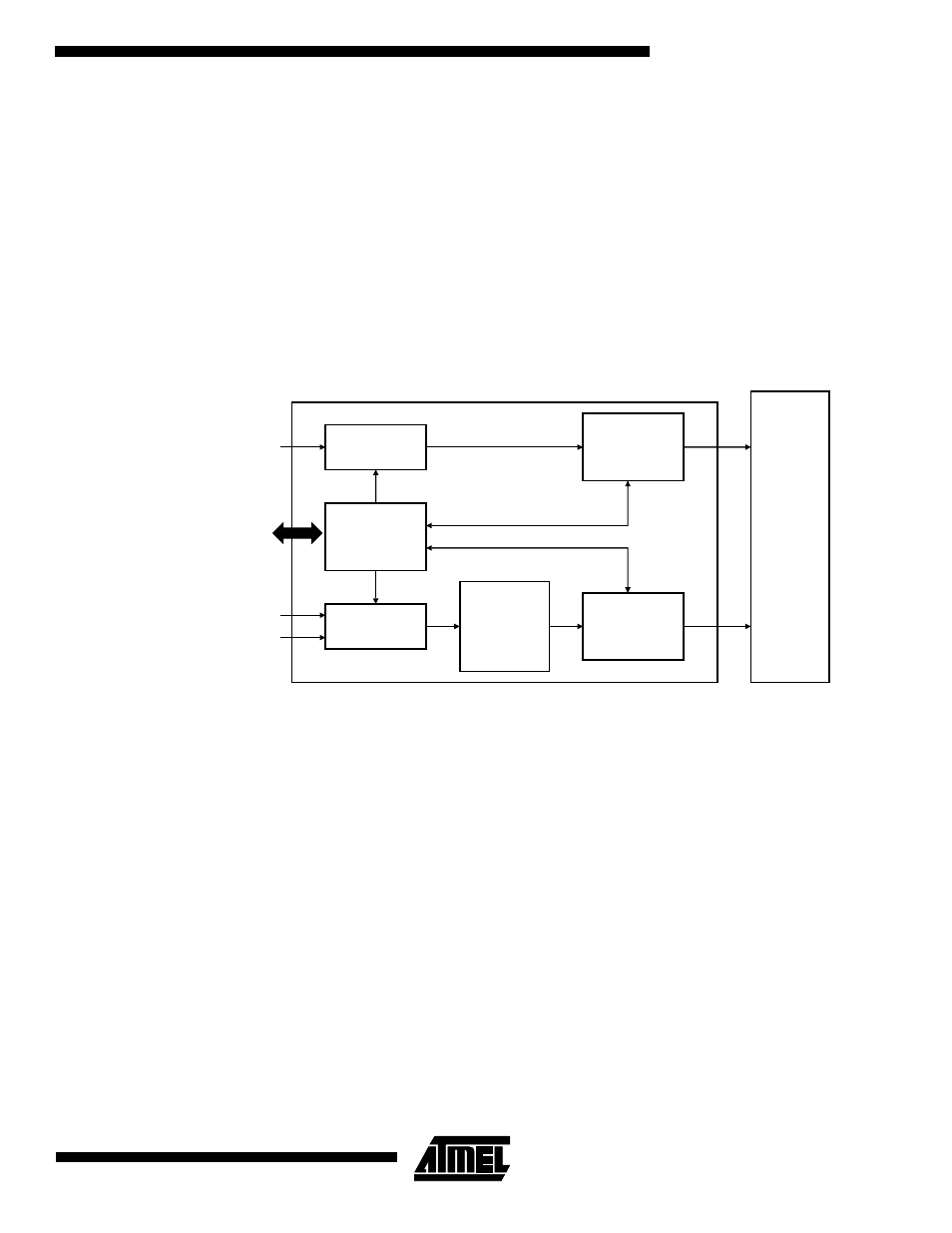

Figure 7. Interrupt Controller Block Diagram

Note:

After a hardware reset, the AIC pins are controlled by the PIO controller. They must be configured to be controlled by the periph-

eral before being used.

Control

Logic

Memorization

Memorization

Prioritization

Controller

NIRQ

Manager

NFIQ

Manager

FIQ Source

Advanced Peripheral

Bus (APB)

Internal Interrupt Sources

External Interrupt Sources

ARM7TDMI

Core

NFIQ

NIRQ