Dmc: dynamic memory controller, Dmc operation, Initialization sequence – Rainbow Electronics AT75C310 User Manual

Page 24: Data alignment

AT75C310

24

DMC: Dynamic Memory Controller

The ARM can access external DRAM by means of the

DRAM memory controller. The DMC sits on the ASB bus

and provides a glueless memory interface to external EDO

DRAM using the common address and data buses.

The AT75C310 supports two DRAM memory regions, each

with its own RAS signal. Both DRAM regions share the

same CAS, OE, WE, address and data signals.

The DRAM controller is programmed as an internal periph-

eral that has a standard APB bus interface and a set of

memory-mapped registers.

The DMC is designed to operate with extended data-out

(EDO) DRAM. It supports two 16-MByte address spaces

and a programmable 16- or 32-bit data bus. The controller

multiplexes the processor address to form DRAM row and

column addresses. The row and column addresses can be

configured to support various combinations of DRAM mem-

ory size, page size and data bus width.

The DMC supports:

•

One or two DRAM memory regions

•

DRAM memory region size of 2, 4, 8 or 16 megabytes

•

DRAM page size of 256, 512, 1024 or 2048 columns

•

Up to 15 row- and 11 column-address bits

•

Asymmetric row and column addressing

•

16- or 32-bit DRAM data bus

•

Automatic page breaking of burst accesses

•

Automatic CAS-before-RAS refresh on timer trigger

•

Automatic power-up initialization sequence

DMC Operation

The DMC multiplexes the ASB address to DRAM row and

column addresses. The column address must be between

eight and eleven bits. The row address is the required num-

ber of higher-order bits to support all combinations of per-

mitted page- and memory-region sizes and both data bus

widths.

The DMC automatically inserts precharge and RAS cycles

and supplies an updated row address to the DRAM when a

sequential burst access from an ASB bus master crosses a

DRAM page boundary. The necessary number of wait

states is inserted to hold the bus master during the pre-

charge and RAS cycles.

The DMC performs a CAS-before-RAS refresh cycle on

both DRAM memory regions on the rising edge of a trigger

signal from the AT75C310 on-chip timer. If the DMC is per-

forming a DRAM access when the trigger occurs, the

access will finish before the refresh operation is performed.

In the case of a burst access, the refresh is not performed

until the end of the burst.

The DMC is capable of limiting the length of a burst access

if a refresh trigger has been received. If the feature is

enabled, the DMC performs the refresh operation once it

has been pending for 32 accesses in a burst sequence.

The DMC includes the functionality to interface the 32-bit

ASB data bus with a 16-bit DRAM data bus. It automatically

performs two accesses to the DRAM to service a 32-bit

access from the ASB.

Initialization Sequence

The DMC performs eight CAS-before-RAS refresh opera-

tions to both DRAM banks at the end of the AT75C310

reset pulse. The processor is not required to perform any

DRAM initialization operations. However, it is required to

initialize the DMC.

Data Alignment

The DMC only supports accesses to the appropriate data

boundary, i.e., word accesses must be word-aligned and

half-word accesses must be half-word-aligned. Misaligned

accesses will be ignored by the DMC, and the AMBA

decoder will therefore flag an abort to the appropriate ASB

bus master.

The ARM processor does not guarantee the level of the

bottom two address bits for an instruction access in ARM

state or the bottom address bit for an instruction fetch in

Thumb state. Therefore, the DMC will service misaligned

instruction fetches and force alignment, e.g., a 16-bit

instruction fetch from address 0x00000003 is performed as

a 16-bit read of address 0x00000002.

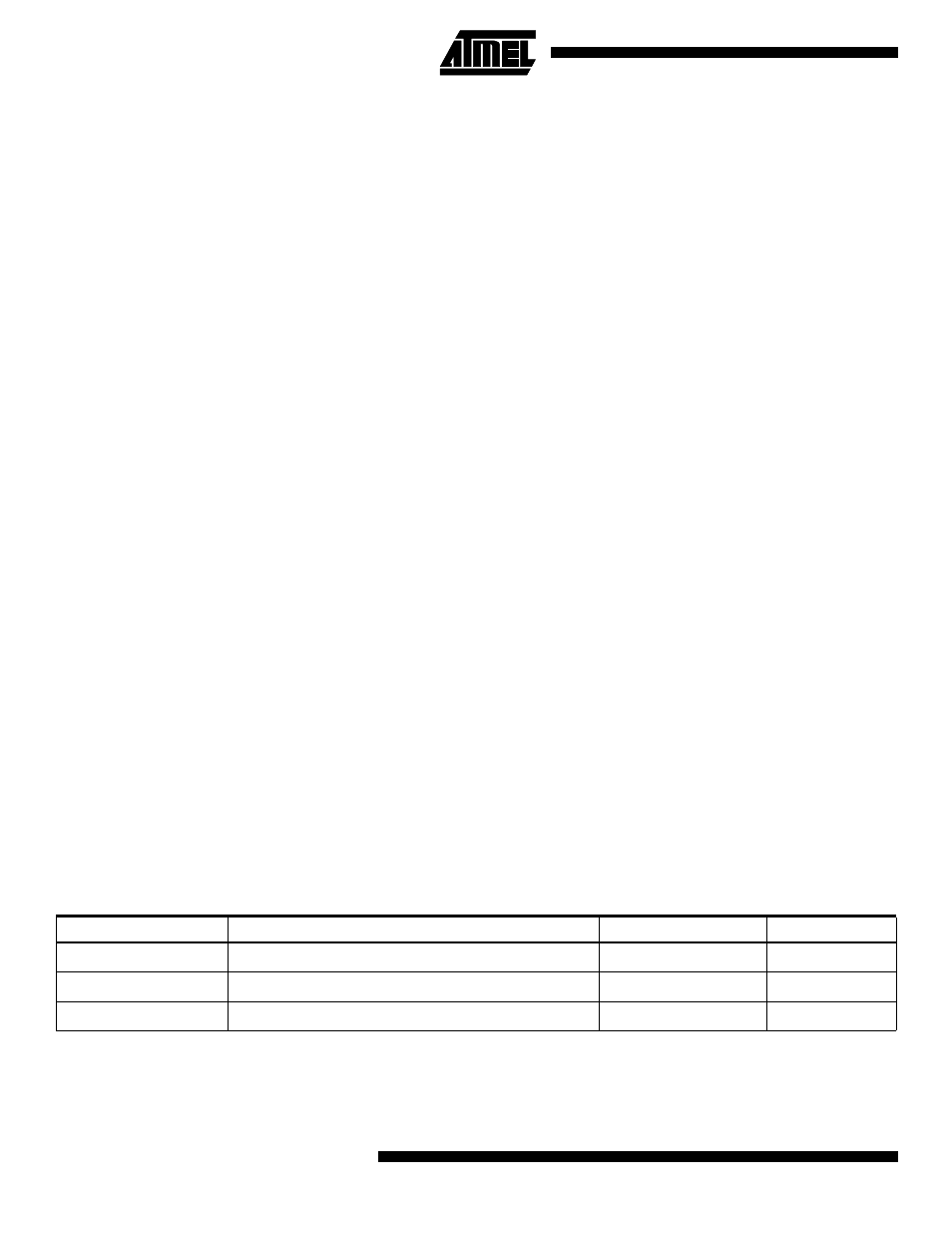

Table 9. DMC Register Map

Register Offset

Register Description

Register Name

Access

0x0

DRAM Region 0 Configuration Register

DMC_MR0

Read/write

0x4

DRAM Region 1 Configuration Register

DMC_MR1

Read/write

0x8

DRAM Common Configuration Register

DMC_CR

Read/write