Signal interface, Data bus width, Byte-write or byte-select mode – Rainbow Electronics AT75C310 User Manual

Page 16

AT75C310

16

Signal Interface

Data Bus Width

A data bus width of 32 or 16 bits can be selected for each

chip select. This option is controlled by the DBW field in the

Chip Select Register (SMC_CSR) of the corresponding

chip select.

The AT75C310 always boots up with a data bus width of 16

bits set in SMC_CSR0.

Byte-write or Byte-select Mode

Each chip select with a 32-/16-bit data bus operates with

one or two different types of write mode:

1.

Byte-write mode supports four (32-bit bus) or two

(16-bit bus) byte writes and a single read signal.

2.

Byte-select mode selects the appropriate byte(s)

using four (32-bit bus) or two (16-bit bus) byte-select

lines and separate read and write signals.

This option is controlled by the BAT field in SMC_CSR for

the corresponding chip select.

Byte-write access can be used to connect four 8-bit devices

as a 32-bit memory page or two 8-bit devices as a 16-bit

memory page.

For a 32-bit bus:

•

The signal NWE0 is used as the write enable signal for

byte 0.

•

The signal NWE1 is used as the write enable signal for

byte 1.

•

The signal NWE2 is used as the write enable signal for

byte 2.

•

The signal NWE3 is used as the write enable signal for

byte 3.

•

The signal NSOE enables memory reads to all memory

blocks.

For a 16-bit bus:

•

The signal NWE0 is used as the write enable signal for

byte 0.

•

The signal NWE1 is used as the write enable signal for

byte 1.

•

The signal NSOE enables memory reads to all memory

blocks.

Byte-select mode can be used to connect one 32-bit device

or two 16-bit devices in a 32-bit memory page or one 16-bit

device in a 16-bit memory page.

For a 32-bit bus:

•

The signal NWE0 is used to select byte 0 for read and

write operations.

•

The signal NWE1 is used to select byte 1 for read and

write operations.

•

The signal NWE2 is used to select byte 2 for read and

write operations.

•

The signal NWE3 is used to select byte 3 for read and

write operations.

•

The signal NWR is used as the write enable signal for

the memory block.

•

The signal NSOE enables memory reads to the memory

block.

For a 16-bit bus:

•

The signal NWE0 is used to select byte 0 for read and

write operations.

•

The signal NWE1 is used to select byte 1 for read and

write operations.

•

The signal NWR is used as the write enable signal for

the memory block.

•

The signal NSOE enables memory reads to the memory

block.

During boot, the number of external devices (number of

active chip selects) and their configurations must be pro-

grammed as required. The chip select addresses that are

programmed take effect immediately. Wait states also take

effect immediately when they are programmed to optimize

boot program execution.

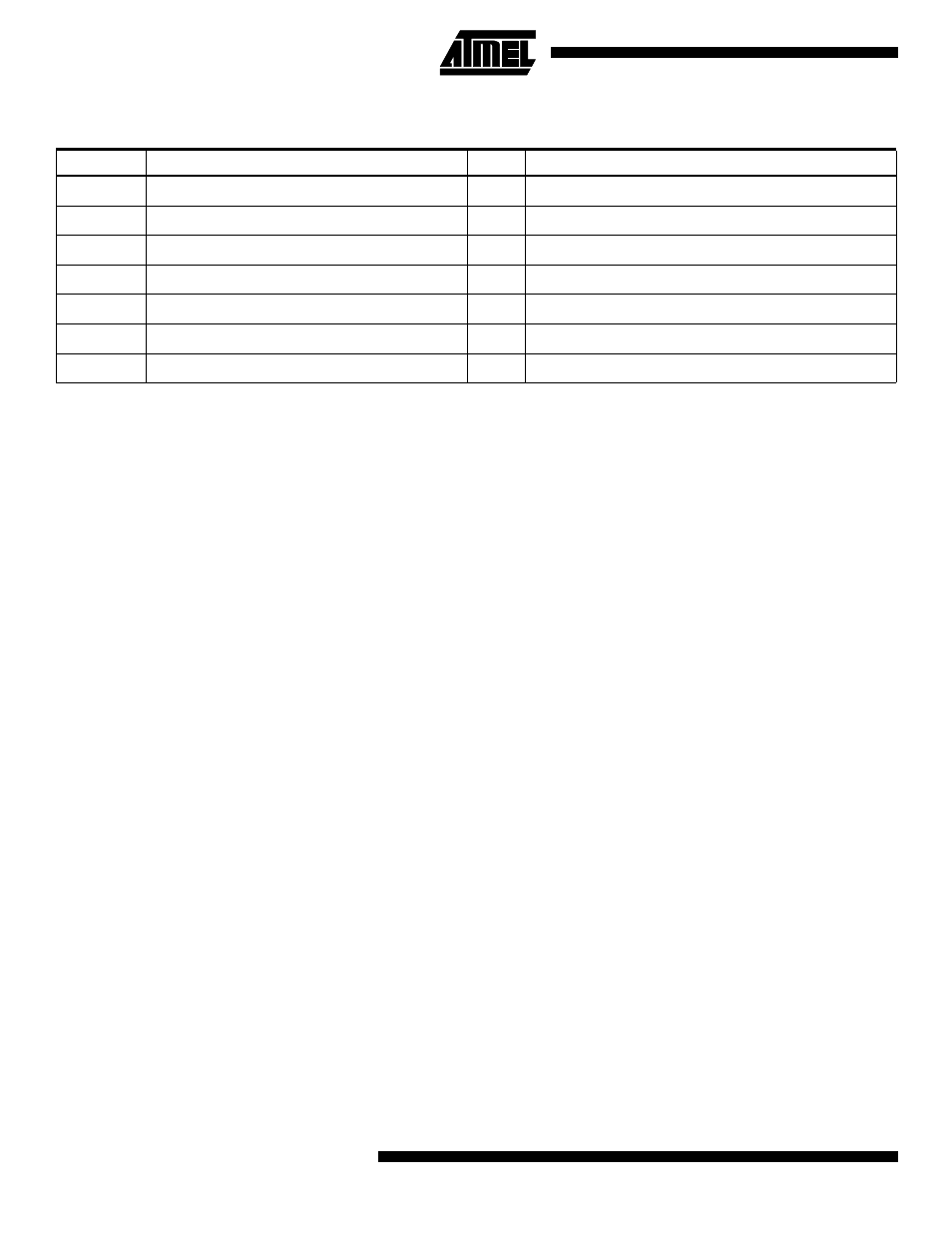

Table 6. Signal Interface

FPDRAM

Description

Type

Notes

A[23:0]

Address bus

O

D[31:0]

Data bus

I/O

D[15:0] used when Data Bus Width is 16

NCE[3:0]

Active low chip enables

O

NCE[3] can be configured for LCD interface mode

NWE[3:0]

Active low byte select/write strobe signals

O

NWR

Active low write strobe signals

O

NSOE

Active low read enable signal

O

NWAIT

Active low wait signal

I