Xilinx Virtex-5 FPGA ML561 User Manual

Page 97

Virtex-5 FPGA ML561 User Guide

97

UG199 (v1.2.1) June 15, 2009

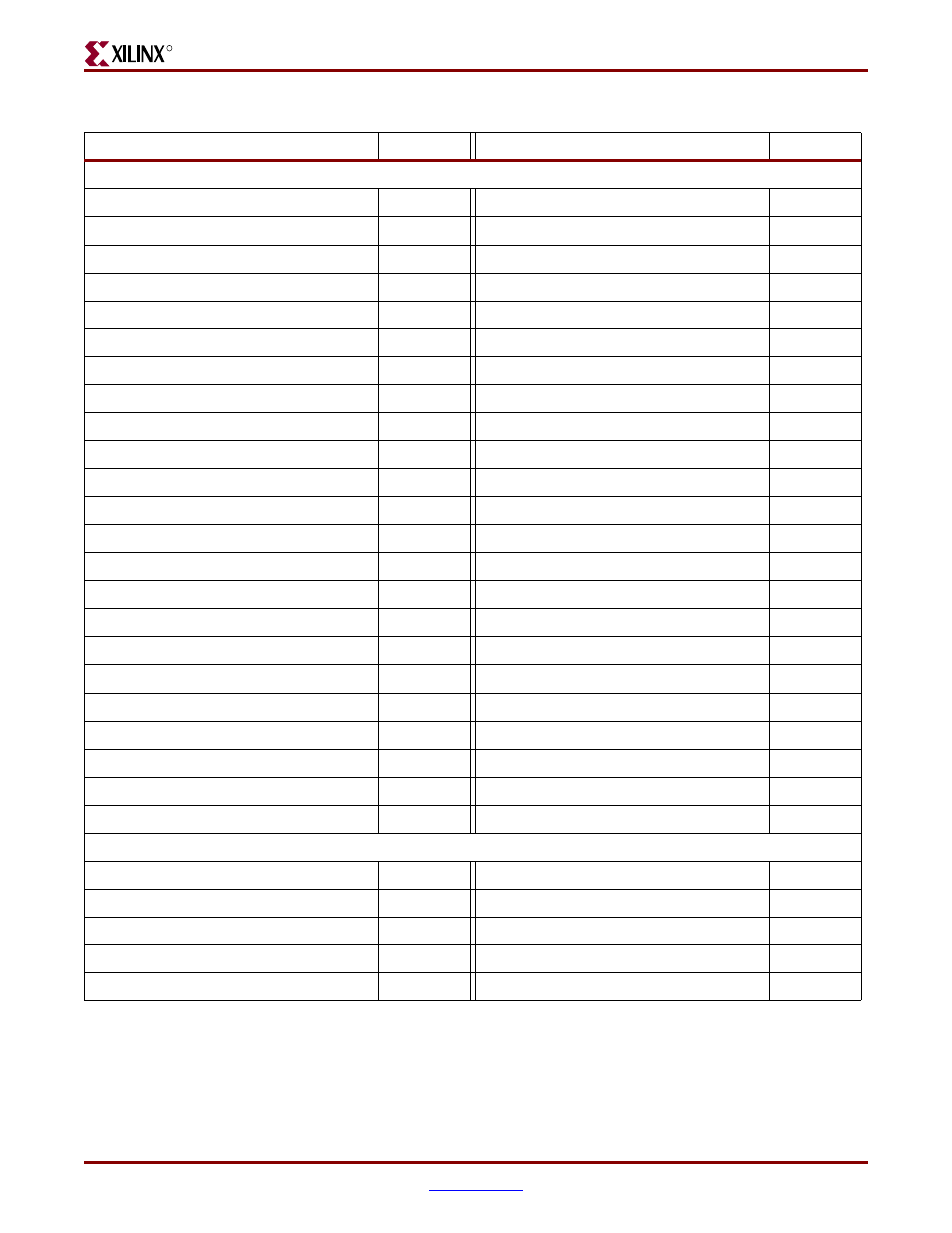

FPGA #1 Pinout

R

DDR2 Component Interface (cont.)

DDR2_WE_N J21

DDR2_DQ_BY2_B2

N25

DDR2_DM_BY0 U30

DDR2_DQ_BY2_B3

P25

DDR2_DM_BY1 L29

DDR2_DQ_BY2_B4

P24

DDR2_DM_BY2 K27

DDR2_DQ_BY2_B5

N24

DDR2_DM_BY3 J27

DDR2_DQ_BY2_B6

P27

DDR2_DQ_BY0_B0 T25

DDR2_DQ_BY2_B7 P26

DDR2_DQ_BY0_B1 U25

DDR2_DQ_BY3_B0 M26

DDR2_DQ_BY0_B2 T26

DDR2_DQ_BY3_B1 M25

DDR2_DQ_BY0_B3 U26

DDR2_DQ_BY3_B2 J25

DDR2_DQ_BY0_B4 R27

DDR2_DQ_BY3_B3 J24

DDR2_DQ_BY0_B5 R26

DDR2_DQ_BY3_B4 L26

DDR2_DQ_BY0_B6 U28

DDR2_DQ_BY3_B5 L25

DDR2_DQ_BY0_B7 U27

DDR2_DQ_BY3_B6 L24

DDR2_DQ_BY1_B0 E31

DDR2_DQ_BY3_B7 K24

DDR2_DQ_BY1_B1 F31

DDR2_DQS_BY0_N N30

DDR2_DQ_BY1_B2 J29

DDR2_DQS_BY0_P M31

DDR2_DQ_BY1_B3 H29

DDR2_DQS_BY1_N P29

DDR2_DQ_BY1_B4 F30

DDR2_DQS_BY1_P N29

DDR2_DQ_BY1_B5 G30

DDR2_DQS_BY2_N E27

DDR2_DQ_BY1_B6 F29

DDR2_DQS_BY2_P E26

DDR2_DQ_BY1_B7 E29

DDR2_DQS_BY3_N H27

DDR2_DQ_BY2_B0 T24

DDR2_DQS_BY3_P G27

DDR2_DQ_BY2_B1 23

R24

FPGA #1 Clock and Reset Signals

CLK_TO_FPGA1_MGT_116_N H3

DIRECT_CLK_TO_FPGA1_P AG22

CLK_TO_FPGA1_MGT_116_P H4

EXT_CLK_TO_FPGA1_N AG13

CLK_TO_FPGA1_MGT_118_N AF3

EXT_CLK_TO_FPGA1_P AH12

CLK_TO_FPGA1_MGT_118_P AF4

FPGA1_LOW_FREQ_CLK AH20

DIRECT_CLK_TO_FPGA1_N AH22

FPGA1_RESET_N

AH14

Table A-1:

FPGA #1 Pinout (Continued)

Signal Name

Pin

Signal Name

Pin