Fpga pinouts, Fpga #1 pinout, Appendix a: fpga pinouts – Xilinx Virtex-5 FPGA ML561 User Manual

Page 95: Appendix a, “fpga pinouts, For a com, Appendix a, “fpga, Pinouts, Appendix a

Virtex-5 FPGA ML561 User Guide

95

UG199 (v1.2.1) June 15, 2009

R

Appendix A

FPGA Pinouts

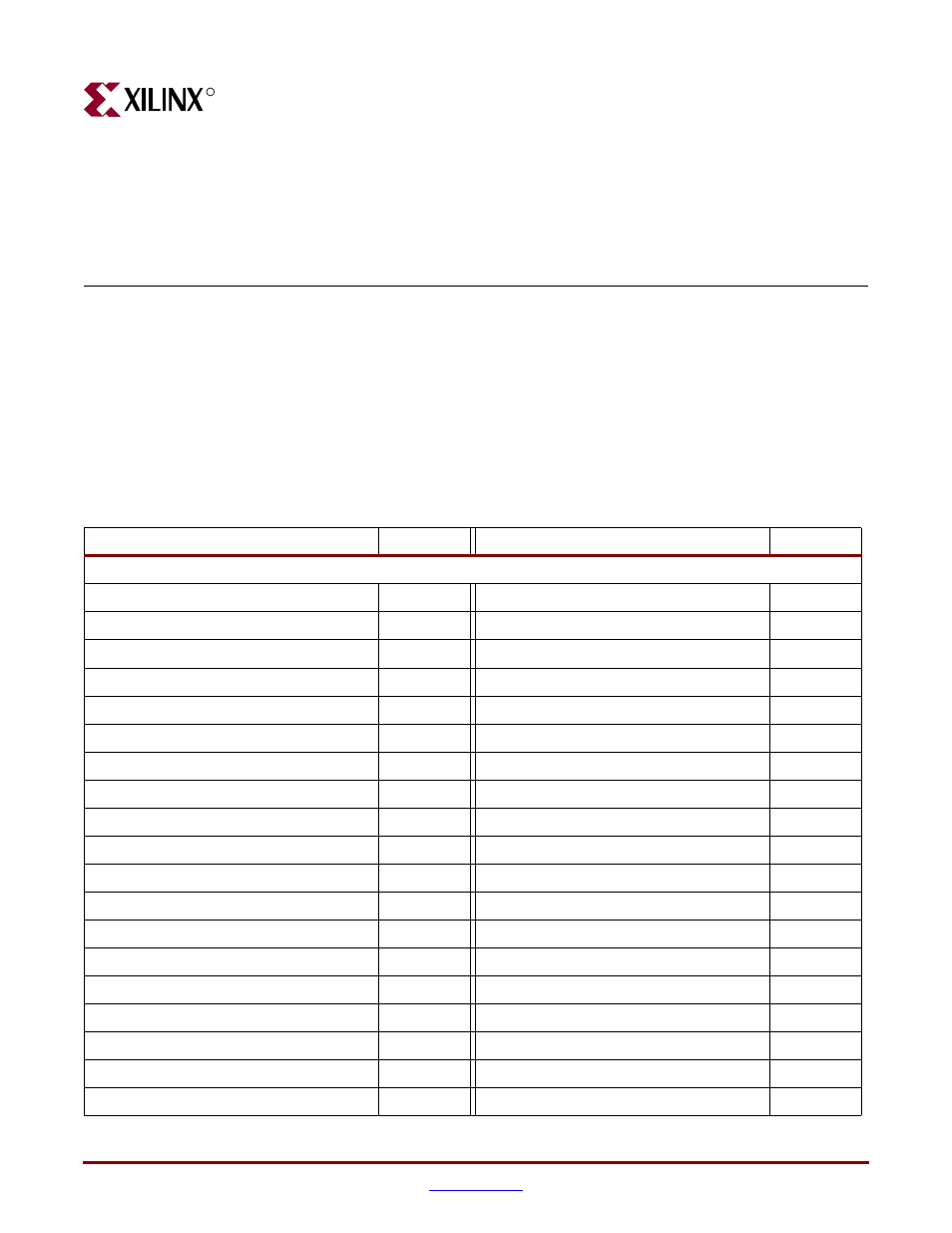

This appendix provides the pinouts for the three FPGAs on the Virtex-5 FPGA ML561

Development Board. The toolkit CD shipped with every ML561 contains sample UCFs for

each memory interface. These UCFs are for pinout reference only and do not include other

constraints, like I/O standards.

FPGA #1 Pinout

lists the connections for FPGA #1 (U7).

Table A-1:

FPGA #1 Pinout

Signal Name

Pin

Signal Name

Pin

DDR400 Component Interface

DDR1_A0 M32

DDR1_CK1_N

AJ34

DDR1_A1 L33

DDR1_CK1_P

AH34

DDR1_A10 E33

DDR1_CK2_N

AE34

DDR1_A11 E32

DDR1_CK2_P

AF34

DDR1_A12 E34

DDR1_CKE

AC34

DDR1_A13 F33

DDR1_LB_BK11

N32

DDR1_A2 K32

DDR1_LB_BK11

P32

DDR1_A3 K34

DDR1_LB_BK13

AJ32

DDR1_A4 L34

DDR1_LB_BK13

AK32

DDR1_A5 J34

DDR1_RAS_N

AB32

DDR1_A6 H34

DDR1_WE_N

AD34

DDR1_A7 H33

DDR1_DM_BY0

AG32

DDR1_A8 F34

DDR1_DM_BY1

Y32

DDR1_A9 G33

DDR1_DM_BY2

P34

DDR1_BA0 AK33

DDR1_DM_BY3

G32

DDR1_BA1 AK34

DDR1_DQ_BY0_B0

AP32

DDR1_BY0_1_CS_N AB33

DDR1_DQ_BY0_B1 AN32

DDR1_BY2_3_CS_N AC33

DDR1_DQ_BY0_B2 AN33

DDR1_CAS_N AC32

DDR1_DQ_BY0_B3

AN34