Xilinx Virtex-5 FPGA ML561 User Manual

Page 43

Virtex-5 FPGA ML561 User Guide

43

UG199 (v1.2.1) June 15, 2009

Power Consumption

R

current can support a voltage swing of up to (16 mA * 50

Ω) = 800 mV, which is sufficient to

meet the output voltage specifications for SSTL18, SSTL2, and HSTL18 I/O standards.

separates the power consumption information from

according to the

nine TI power modules for the first set of nine power planes and the three Fairchild

regulators for the V

TT

power planes. The positive values in the Excess Power column of

show that each of the 14 modules can supply the necessary power for the

corresponding power plane.

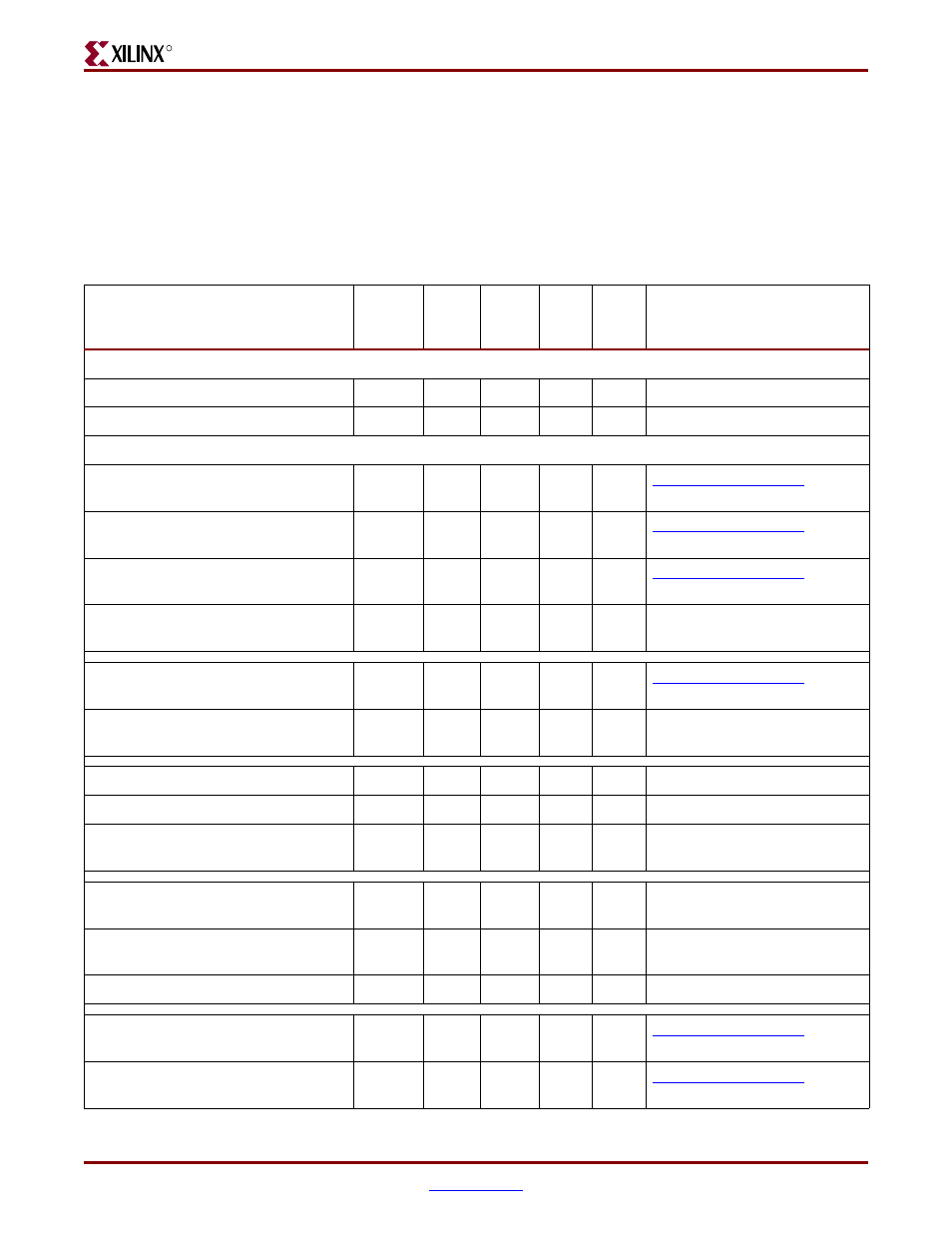

Table 4-3:

ML561 Power Plane Capacities

Device Description

Quantity

Voltage

(V)

Current

(mA)

Power

(W)

Excess

Power

(W)

Source

Total Available Power

5V Power Supply

1

5.0

8000

40.0

Bellus Power SPD-050-5

12V Power Supply

1

12.0

5000

60.0

CUI DTS120500U

Power Consumed by Power Plane

XC5VLX50T-FFG1136: FPGA #1

(DDR400, DDR2)

1

1.0

2289

2.3

XC5VLX50T-FFG1136: FPGA #2

(DDR2 DIMM)

1

1.0

1945

1.9

XC5VLX50T-FFG1136: FPGA #3

(QDRII and RLDRAM II)

1

1.0

2675

2.7

V

CCINT

Power Plane (1.0V) Capacity

1

1.0

15000

15.0

8.1

TI PTH05010 15A Module Data

Sheet

XC5VLX50T-FFG1136: FPGA #3

(QDRII and RLDRAM II)

1

1.8

3876

7.0

HSTL FPGA Power Plane (1.8V)

Capacity

1

1.8

15000

27.0

20.0

TI PTH05010 15A Module Data

Sheet

QDRII Memory [H]

2

1.8

950

3.4

Samsung QDRII Data Sheet

RLDRAM II Memory

2

1.8

920

3.3

Micron RLDRAM II Data Sheet

HSTL_Mem Power Plane (1.8V)

Capacity

1

1.8

6000

10.8

4.1

TI PTH05000 6A Module Data

Sheet

QDRII V

TT

Termination

175

1.0

16

2.8

All signals.

± 500 mV swing

around V

TT

.

RLDRAM II V

TT

Termination

60

1.0

16

1.0

All signals.

± 500 mV swing

around V

TT

.

HSTL _VREF Power Plane (0.9V)

1

0.9

3000

2.7

-0.1

Fairchild FN6555 Data Sheet

XC5VLX50T-FFG1136:

FPGA #1 (DDR2)

1

1.8

1011

1.8

XC5VLX50T-FFG1136:

FPGA #2 (DDR2 DIMM)

1

1.8

4258

7.7