Chapter 7: ml561 hardware-simulation correlation – Xilinx Virtex-5 FPGA ML561 User Manual

Page 72

72

Virtex-5 FPGA ML561 User Guide

UG199 (v1.2.1) June 15, 2009

Chapter 7: ML561 Hardware-Simulation Correlation

R

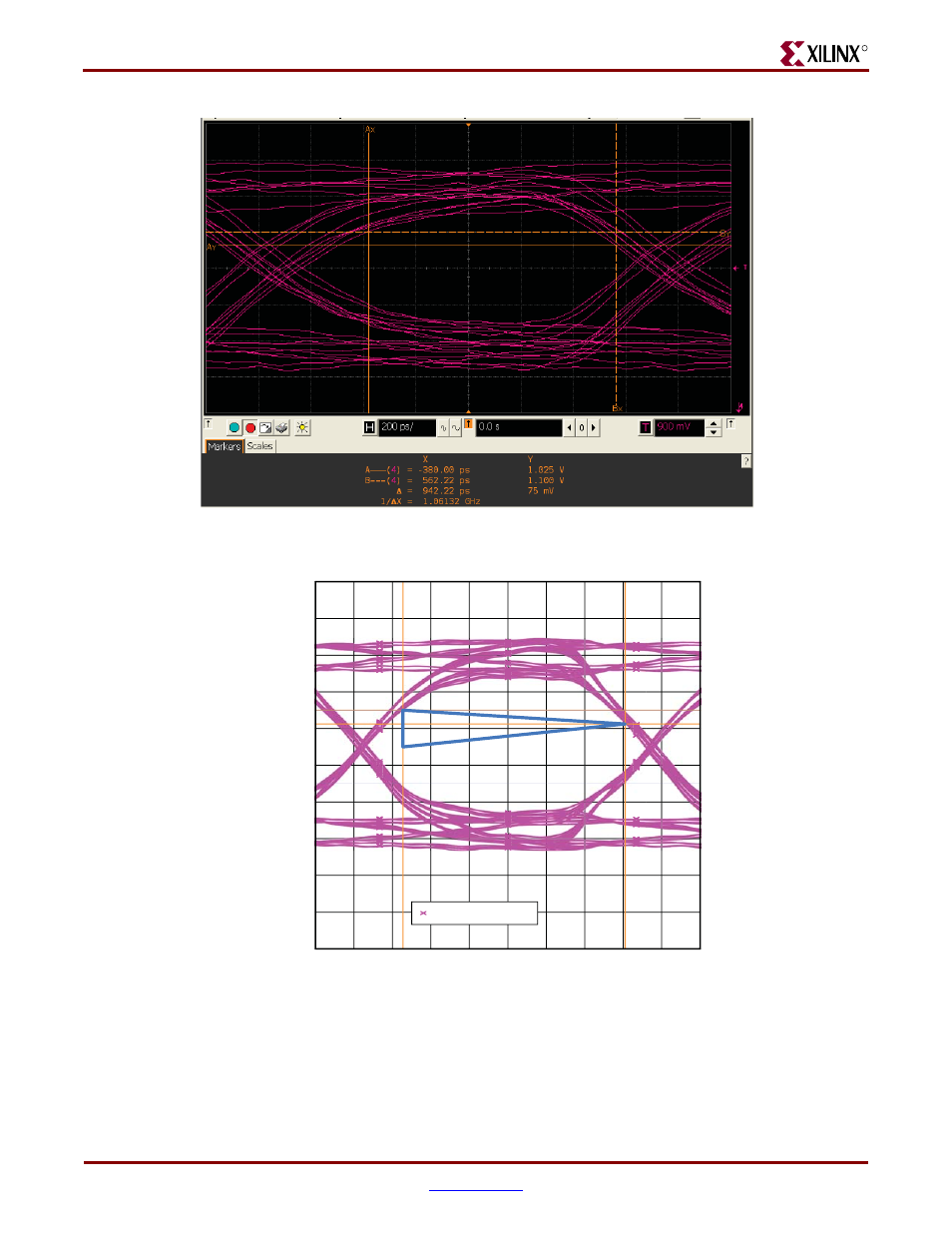

Figure 7-22:

DDR2 DIMM Write HW Measurement - Eye Scope Shot at Probe Point #1 (DDR2 Memory Via)

UG199_c7_22_071107

Figure 7-23:

DDR2 DIMM Write Correlation - Eye Scope Shot at Probe Point #1 (Slow Corner)

800.0

1200.0

1600.0

2000.0

2400.0

2800.0

-200.0

0.000

200.0

400.0

600.0

800.0

1000.0

1200.0

1400.0

1600.0

1800.0

UG199_c7_23_070907

Time (ps)

Voltage (mV)

Probe 3:C13.1 (at pin)

♦

333 MHz, Slow, PRBS6, 77% UI

♦

Cursor 1: 1.1004V, 1.2553 ns

♦

Cursor 2: 1.0253V, 2.4105 ns

♦

Delta Voltage = 75.2 mV, Delta Time = 1.1582 ns (77% UI)