Fpga internal power budget – Xilinx Virtex-5 FPGA ML561 User Manual

Page 46

46

Virtex-5 FPGA ML561 User Guide

UG199 (v1.2.1) June 15, 2009

Chapter 4: Electrical Requirements

R

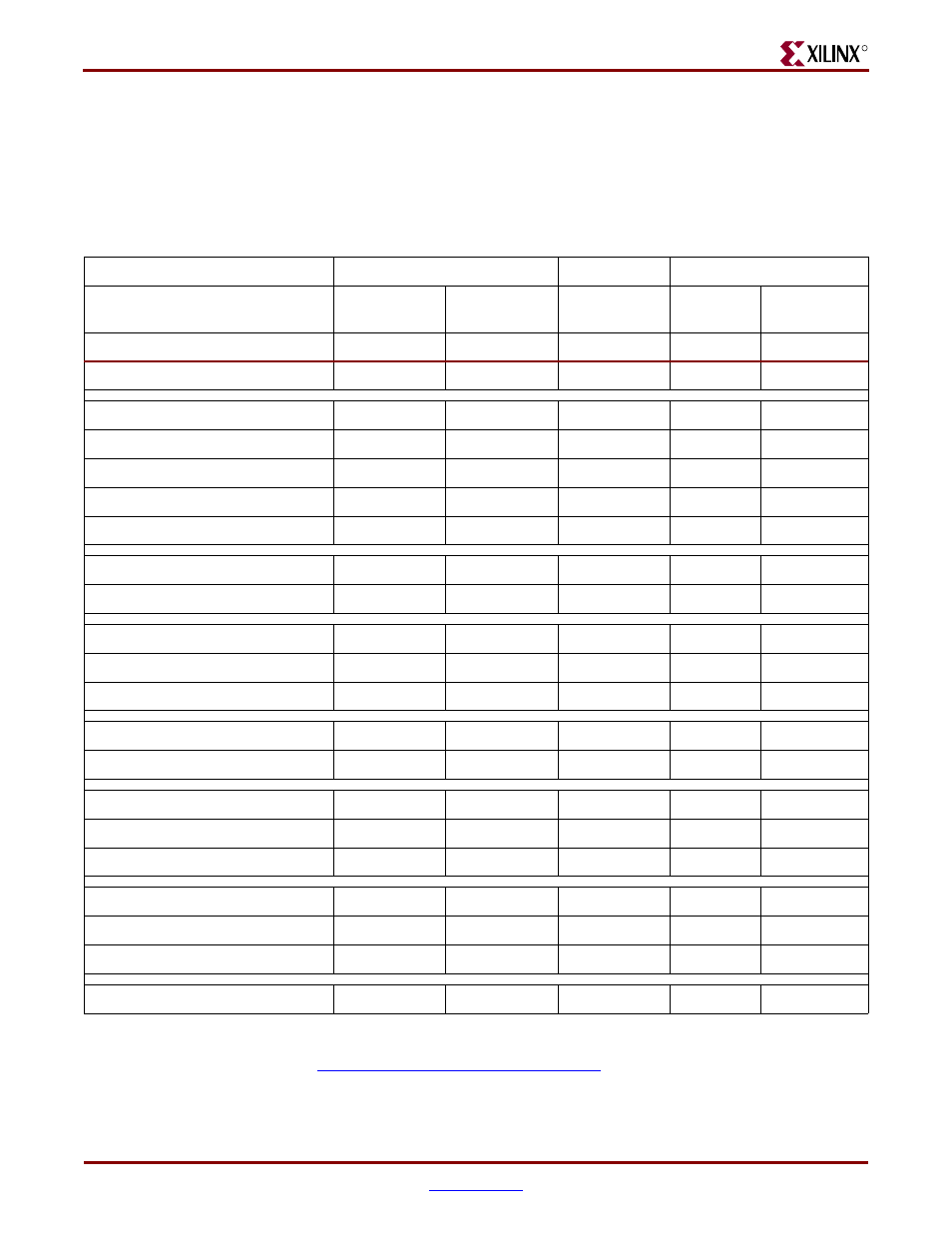

FPGA Internal Power Budget

summarizes power consumption estimates by each of the three

XC5VLX50T-FFG1136 FPGAs on the Virtex-5 FPGA ML561 Development Board. This

estimate derives the FPGA utilization information from the respective map report of a fully

configured reference design.

Table 4-4:

ML561 FPGA Power Estimate Summary

FPGA #

FPGA #1

FPGA #2

(1)

FPGA #3

Interface

DDR400 Comp

(DCI)

DDR2 Comp

(DCI)

DDR2 DIMM

(DCI)

QDRII (DCI)

RLDRAM II

(DCI)

I/O Standard

SSTL_18

HSTL_18

HSTL_18

Total Power (W)

3.7

3.1

10.2

6.3

4.5

V

CCINT

(1.0V) mW

763

763

1945

1160

1515

V

CCAUX

(2.5V) mW

435

544

544

544

544

SSTL_18 V

CCO

(1.8V) mW

1819

7664

SSTL_2 V

CCO

(2.6V) mW

2469

HSTL_18 V

CCO

(1.8V) mW

4571

2406

I/O Frequency (MHz)

200

400

400

400

400

Fabric Frequency (MHz)

200

200

200

200

200

Number of Slices

1500

1500

5910

2750

1951

Number of Flip-flops

2000

2000

7352

2000

1800

Number of Shift Register LUTs

50

50

143

750

400

Number of Block RAMs

5

5

17

14

21

Number of DCMs

2

2

2

2

2

Inputs

10

10

10

90

13

Outputs

50

50

90

160

52

Bidirectionals

36

40

192

0

36

Ambient Temperature (°C)

25

25

25

25

25

Airflow (LFM)

0

0

250

250

0

Heat Sink (Theta-J)

n/a

n/a

5

5

n/a

Junction Temperature (°C)

67

60

78

58

76

Notes:

1. For DDR2 DIMMs as well as QDRII memory interfaces with DCI, an MD35E-10B heat sink is needed. A heat sink with Theta-J = 5.0

should be okay without airflow.

for the heat sink profile. A heat sink with

Theta-J = 5.0 might need airflow of 250 LFM.