Xilinx Virtex-5 FPGA ML561 User Manual

Page 13

Virtex-5 FPGA ML561 User Guide

13

UG199 (v1.2.1) June 15, 2009

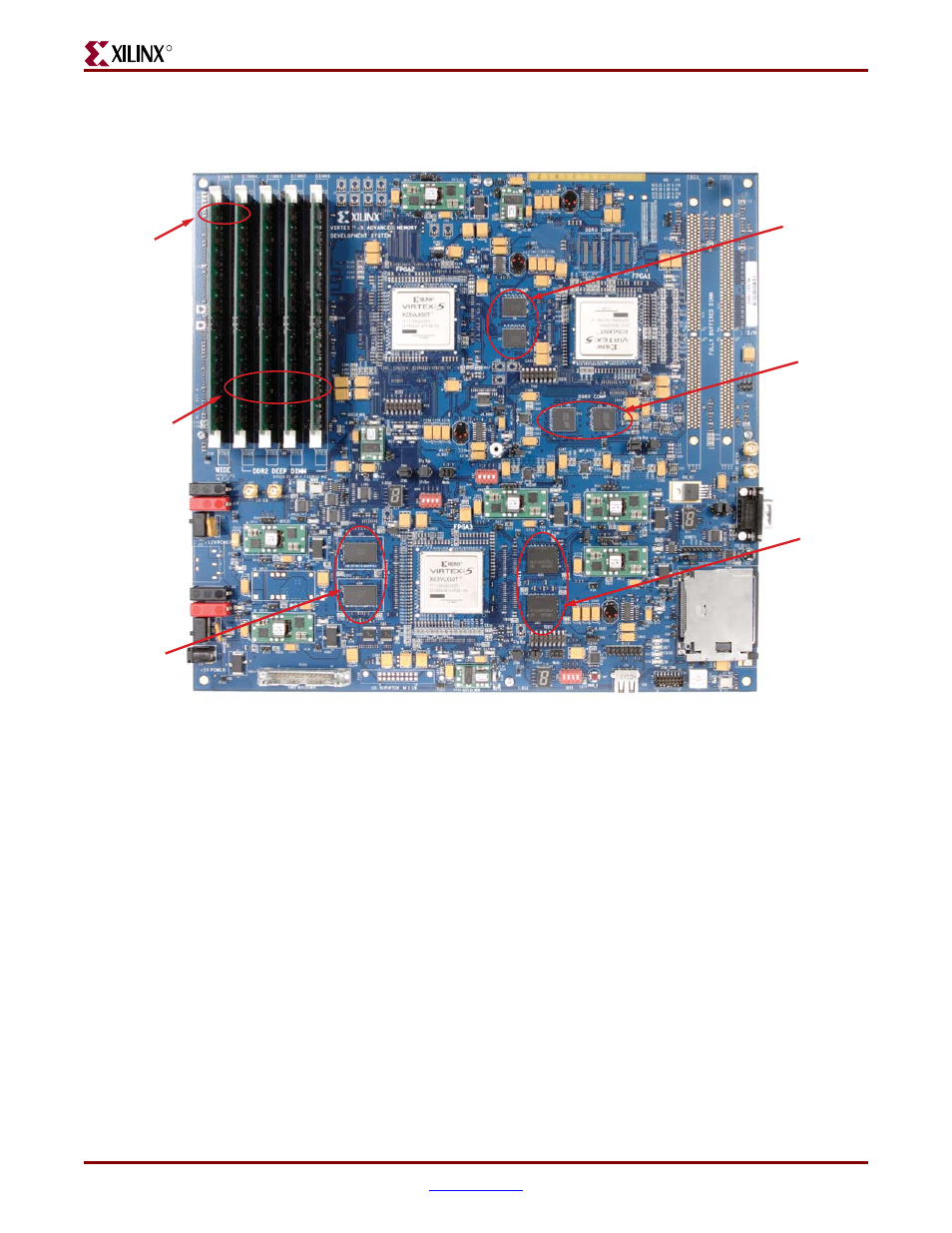

Virtex-5 FPGA ML561 Memory Interfaces Development Board

R

shows the Virtex-5 FPGA ML561 Development Board and indicates the

locations of the resident memory devices.

Figure 1-2:

Virtex-5 FPGA ML561 Development Board

S

A i l N

10 t

hit

/ d

h d

F/L

DDR2

SDRAM

DIMM

32-bit

DDR400

SDRAM

32-bit

DDR2

SDRAM

72-bit

QDRII

SRAM

36-bit

RLDRAM II

144 bits wide

72 bits wide,

up to 4 deep

UG199_c1_02_050106