Xilinx Virtex-5 FPGA ML561 User Manual

Page 96

96

Virtex-5 FPGA ML561 User Guide

UG199 (v1.2.1) June 15, 2009

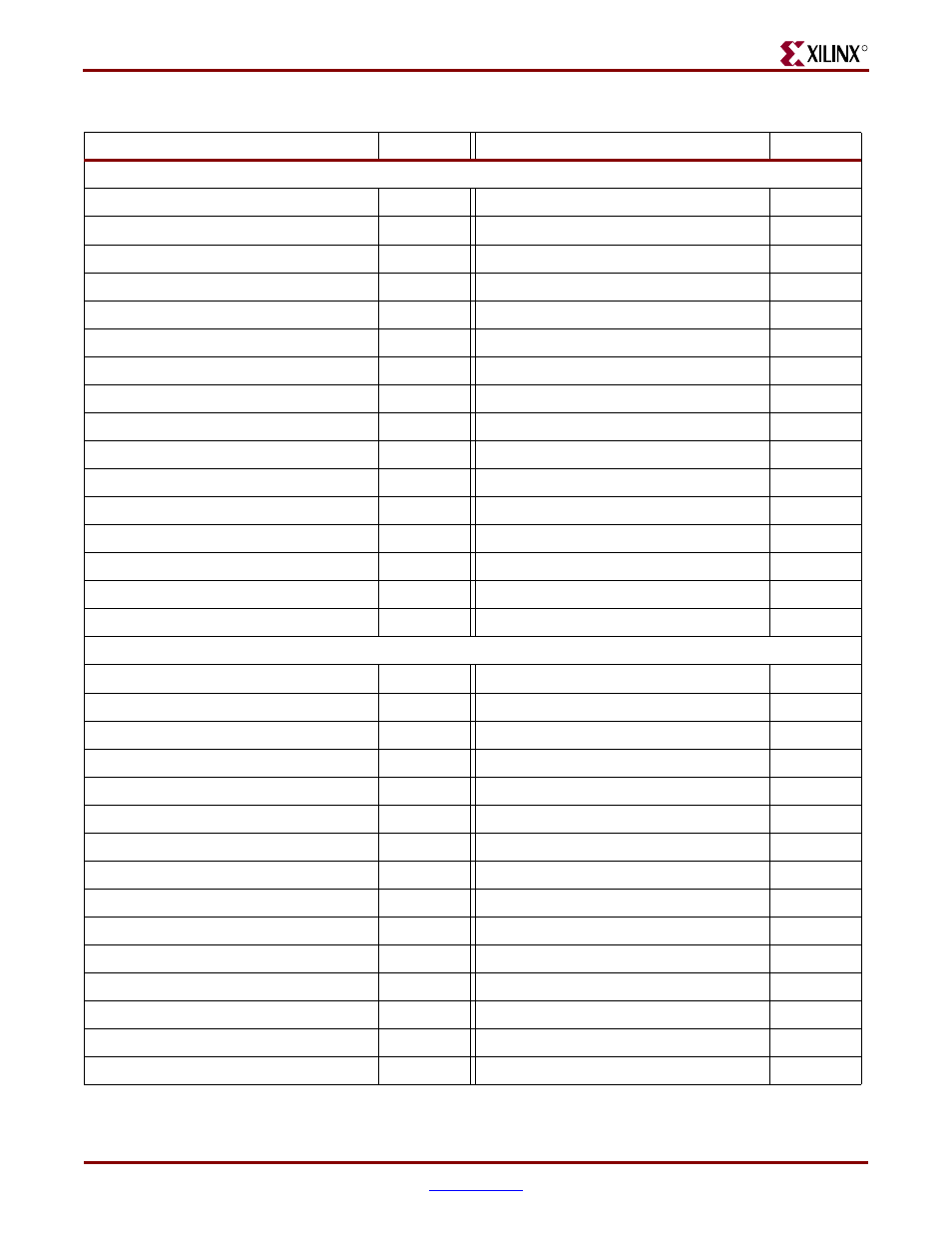

Appendix A: FPGA Pinouts

R

DDR400 Component Interface (cont.)

DDR1_DQ_BY0_B4 AM32

DDR1_DQ_BY2_B4 R32

DDR1_DQ_BY0_B5 AM33

DDR1_DQ_BY2_B5 R33

DDR1_DQ_BY0_B6 AL33

DDR1_DQ_BY2_B6 R34

DDR1_DQ_BY0_B7 AL34

DDR1_DQ_BY2_B7 T33

DDR1_DQ_BY1_B0 Y34

DDR1_DQ_BY3_B0 D34

DDR1_DQ_BY1_B1 AA34

DDR1_DQ_BY3_B1 C34

DDR1_DQ_BY1_B2 AA33

DDR1_DQ_BY3_B2 D32

DDR1_DQ_BY1_B3 Y33

DDR1_DQ_BY3_B3 C32

DDR1_DQ_BY1_B4 V34

DDR1_DQ_BY3_B4 C33

DDR1_DQ_BY1_B5 W34

DDR1_DQ_BY3_B5 B33

DDR1_DQ_BY1_B6 V33

DDR1_DQ_BY3_B6 A33

DDR1_DQ_BY1_B7 V32

DDR1_DQ_BY3_B7 B32

DDR1_DQ_BY2_B0 U31

DDR1_DQS_BY0_P AD32

DDR1_DQ_BY2_B1 U32

DDR1_DQS_BY1_P AF33

DDR1_DQ_BY2_B2 T34

DDR1_DQS_BY2_P K33

DDR1_DQ_BY2_B3 U33

DDR1_DQS_BY3_P J32

DDR2 Component Interface

DDR2_A0 K12

DDR2_CAS_N

J14

DDR2_A1 K13

DDR2_CK0_N

K19

DDR2_A10 G22

DDR2_CK0_P

L19

DDR2_A11 J15

DDR2_CK1_N

J19

DDR2_A12 K16

DDR2_CK1_P

K18

DDR2_A2 H23

DDR2_CKE K17

DDR2_A3 G23

DDR2_CS0_N

H20

DDR2_A4 H12

DDR2_CS1_N

H19

DDR2_A5 J12

DDR2_LB_BK15

T28

DDR2_A6 K22

DDR2_LB_BK15

T29

DDR2_A7 K23

DDR2_LB_BK19

M28

DDR2_A8 K14

DDR2_LB_BK19

N28

DDR2_A9 L14

DDR2_ODT0

H18

DDR2_BA0 K21

DDR2_ODT1 H17

DDR2_BA1 J22

DDR2_RAS_N

H13

Table A-1:

FPGA #1 Pinout (Continued)

Signal Name

Pin

Signal Name

Pin