Table 4-1 – Xilinx Virtex-5 FPGA ML561 User Manual

Page 40

40

Virtex-5 FPGA ML561 User Guide

UG199 (v1.2.1) June 15, 2009

Chapter 4: Electrical Requirements

R

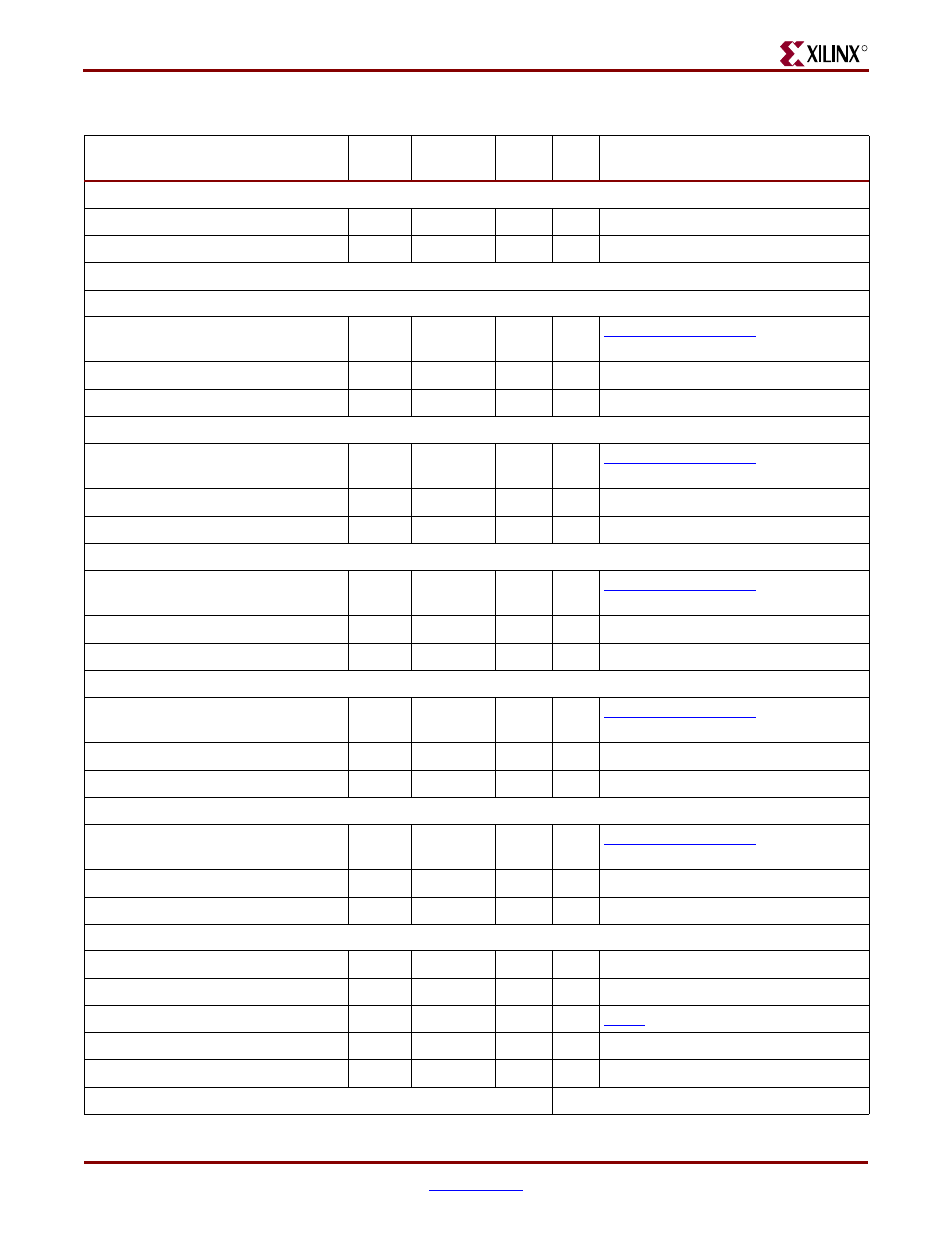

Table 4-1:

ML561 Power Consumption

Device Description

Quantity Voltage (V)

Current

(mA)

Power

(W)

Source

Total Available Power

5V Power Supply

1

5.0

8000

40.0

Bellus Power SPD-050-5

12V Power Supply

1

12.0

5000

60.0

CUI DTS120500U

Power Consumed

DDR400 Component Interface

XC5VLX50T-FFG1136:

FPGA #1 (DDR400)

1

1.0, 2.5, 2.6

1887

3.7

DDR x16 Memory

2

2.6

210

1.1

Micron DDR Component Data Sheet

DDR Comp V

TT

Termination

60

1.2

16

1.2

All signals.

±608 mV swing around V

TT

DDR2 Component Interface

XC5VLX50T-FFG1136:

FPGA #1 (DDR2)

1

1.0, 1.8[S],

2.5

1991

3.1

DDR2 x16 Memory

2

1.8

250

0.9

Micron DDR2 Component Data Sheet

DDR2 Comp V

TT

Termination

25

1.2

16

0.5

Addr/Cntl:

± 603 mV swing around V

TT

DDR2 DIMM Interface

XC5VLX50T-FFG1136:

FPGA #2 (DDR2)

1

1.0, 1.8[S],

2.5

6420

10.2

DDR2 DIMM

2

1.8

1755

6.3

Micron DDR2 DIMM Data Sheet

DDR2 DIMM V

TT

Termination

160

1.2

16

3.1

All signals:

± 603 mV swing around V

TT

QDRII Memory Interface

XC5VLX50T-FFG1136:

FPGA #3 (QDRII)

1

1.0, 1.8[H],

1.8[S], 2.5

3917

6.3

QDRII Memory [H]

2

1.8

950

3.4

Samsung QDRII Data Sheet

QDRII V

TT

Termination

175

1.0

16

2.8

All signals.

± 500 mV swing around V

TT

RLDRAM II Memory Interface

XC5VLX50T-FFG1136:

FPGA #3 (RLDRAM II)

1

1.0, 1.8[H],

2.5

3069

4.5

RLDRAM II Memory

2

1.8

920

3.3

Micron RLDRAM II Data Sheet

RLDRAM II V

TT

Termination

60

1.0

16

1.0

All signals.

± 500 mV swing around V

TT

Miscellaneous Circuit

Clock Buffer

1

3.3

23

0.1

ICS8304 Data Sheet

Differential Clock Buffer

2

3.3

115

0.8

ICS853006 Data Sheet

System ACE Controller

1

3.3

200

0.7

System ACE CompactFlash Solution

200 MHz Oscillator

1

2.5

30

0.1

Epson EG2121CA Data Sheet

33 MHz Oscillator

2

3.3

45

0.3

Epson SG-8002CA Data Sheet

Total Power Consumed

53.2