Xilinx ChipScope PLB46 IBA v1.00a User Manual

Introduction

DS619 April 7, 2009

1

Product Specification

© 2009 Xilinx, Inc. Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the United States and other

countries. All other trademarks are the property of their respective owners.

Introduction

The ChipScope™ PLB Integrated Bus Analyzer (IBA) core

is a specialized bus analyzer core designed to debug embed-

ded systems that contain the IBM CoreConnect™ Processor

Local Bus (PLB) version 4.6. The ChipScope PLB46 IBA

core in EDK is based on a Tcl script that generates an Hard-

ware Description Language (HDL) wrapper to the PLB IBA

and calls the ChipScope Core Generator (Coregen) to gener-

ate the netlist based on user parameters.

The ChipScope PLBv46 IBA is a soft IP core designed for

Xilinx® FPGAs and contains the following features:

•

Probes the master, slave, arbiter, and error status signals

of the PLBv46 bus

•

Probes the PLBv46 OR'ed slave signals

•

Automatically adjusts ports to the PLBv46 bus width

•

Separates master, slave, and error status signals into

independent match units which can be enabled or

disabled by a design parameter

•

Allows independent enabling or disabling of probed

master, slave, and error status signals for data capture

•

Supports trigger port customization by a design

parameter

•

Supports match unit type customization for each trigger

port by a design parameter

•

Supports sample depths from 1024-131,072 on

Virtex™-5 Devices selectable by a design parameter

•

Can probe as few as 1 signals and as many as 1115

signals on a Virtex-5 device

•

Provides a separate input bus to allow a user-defined

input debug port

•

Supports a trigger output indicator pin that can be sent

off chip or to other cores

For more information about the PLBv46 IBA core, refer to

the ChipScope Pro Software and Cores User Guide.

ChipScope PLBv46 IBA

(Bus Analyzer) (v. 1.00a, 1.01a)

DS619 April 7, 2009

Product Specification

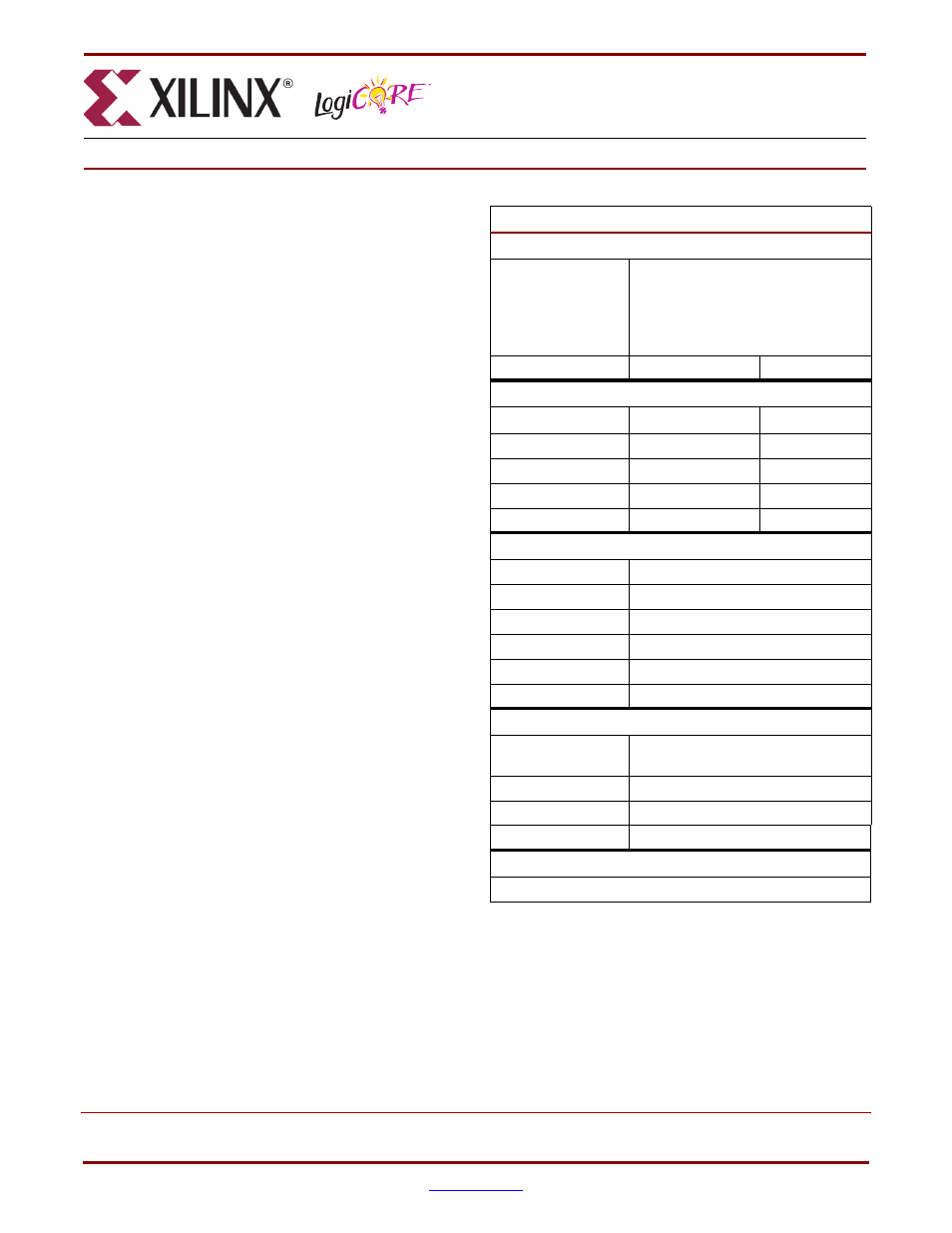

LogiCORE™ Facts

Core Specifics

Supported Device

Family

Spartan®-3, Spartan-3A, Spartan-3AN,

Spartan-3A DSP, Spartan-3E,

Virtex®-4, Virtex-4 FX, Virtex-4 LX,

Virtex-4 SX, Virtex-5 LX,

Virtex-5 LXT, Virtex-5 SXT

Version of Core

chipscope_plb46_iba

v1.00a

Resources Used

Min

Max

Slices

N/A

N/A

LUTs

N/A

N/A

FFs

N/A

N/A

Block RAMs

N/A

N/A

Provided with Core

Documentation

Product Specification

Design File Formats

VHDL/EDIF

Constraints File

N/A

Verification

N/A

Instantiation Template N/A

Reference Designs

None

Design Tool Requirements

Xilinx Implementation

Tools

ISE® 11.1 or later

Verification

ChipScope Pro 11.1 or later

Simulation

Not Supported in Simulation

Synthesis

XST

Support

Provided by Xilinx, Inc.

Document Outline

- ChipScope PLBv46 IBA (Bus Analyzer) (v. 1.00a, 1.01a)

- Introduction

- ChipScope PLB46 IBA I/O Signals

- ChipScope PLB46 IBA Parameters

- Allowable Parameter Combinations

- ChipScope PLB46 IBA Module Block Diagram

- Design Implementation

- Target Technology

- Device Utilization and Performance Benchmarks

- Restrictions

- References

- Support

- Ordering Information

- Revision History

- Notice of Disclaimer