Additional information, Document revision history – Altera Stratix III Development Board User Manual

Page 79

May 2013

Altera Corporation

Stratix III 3SL150 Development Board

Reference Manual

Additional Information

This chapter provides additional information about the document and Altera.

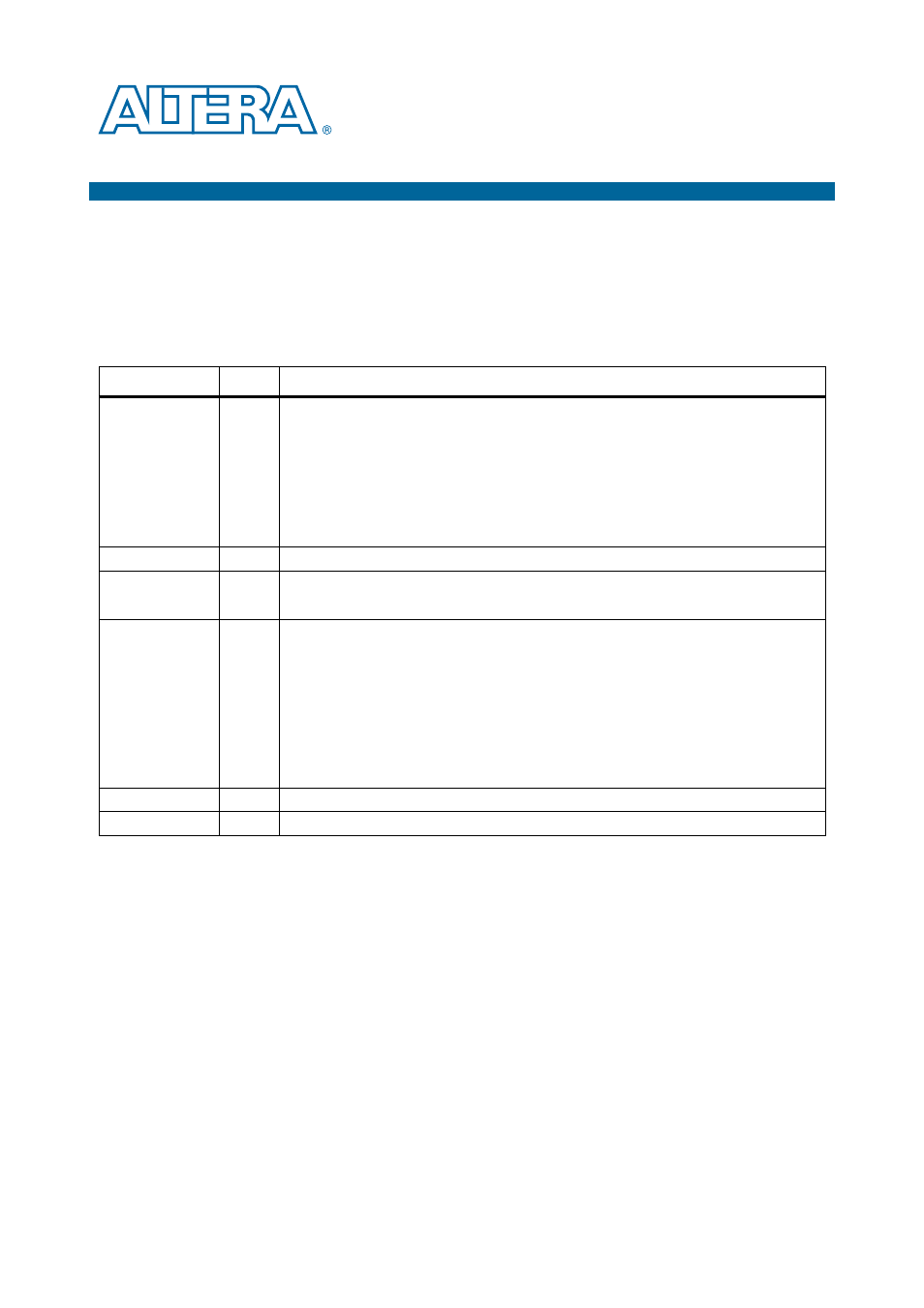

Document Revision History

The following table lists the revision history for this document.

Date

Version

Changes

May 2013

1.5

■

Updated the MAX II pin assignment for FSM_A9 signal in

■

Updated the Stratix III pin numbers for

DDR2_DEVA_A12,DDR2_DEVA_A13,DDR2_DEVA_A14,DDR2_DEVA_BA0,DDR2_DEVA_BA

1,DDR2_DEVA_BA2,

and DDR2_DEVA_CASn signals in

■

Updated the Stratix III pin numbers for DDR2_DEVB_DQ2 and DDR2_DEVB_DQ3 signals in

■

Updated the document template.

November 2008

1.4

■

Updated QDRII interface pin information in

November 2008

1.3

■

Updated DDR2 DIMM board memory size.

■

Updated Stratix III pin numbers for the differential output clock signals in

August 2008

1.2

■

Updated JTAGS settings in

.

■

Updated

section.

■

■

Updated pin description in

.

■

Updated

■

.

■

Corrected pin numbers in

and

March 2008

1.1

Corrected minor errors and incorporated device errata.

December 2007

1.0

First publication