Altera Stratix III Development Board User Manual

Page 45

Chapter 2: Board Components

2–37

General User Interfaces

May 2013

Altera Corporation

Stratix III 3SL150 Development Board

Reference Manual

f

For more information, contact Optrex Am

or New Japan

Radio at

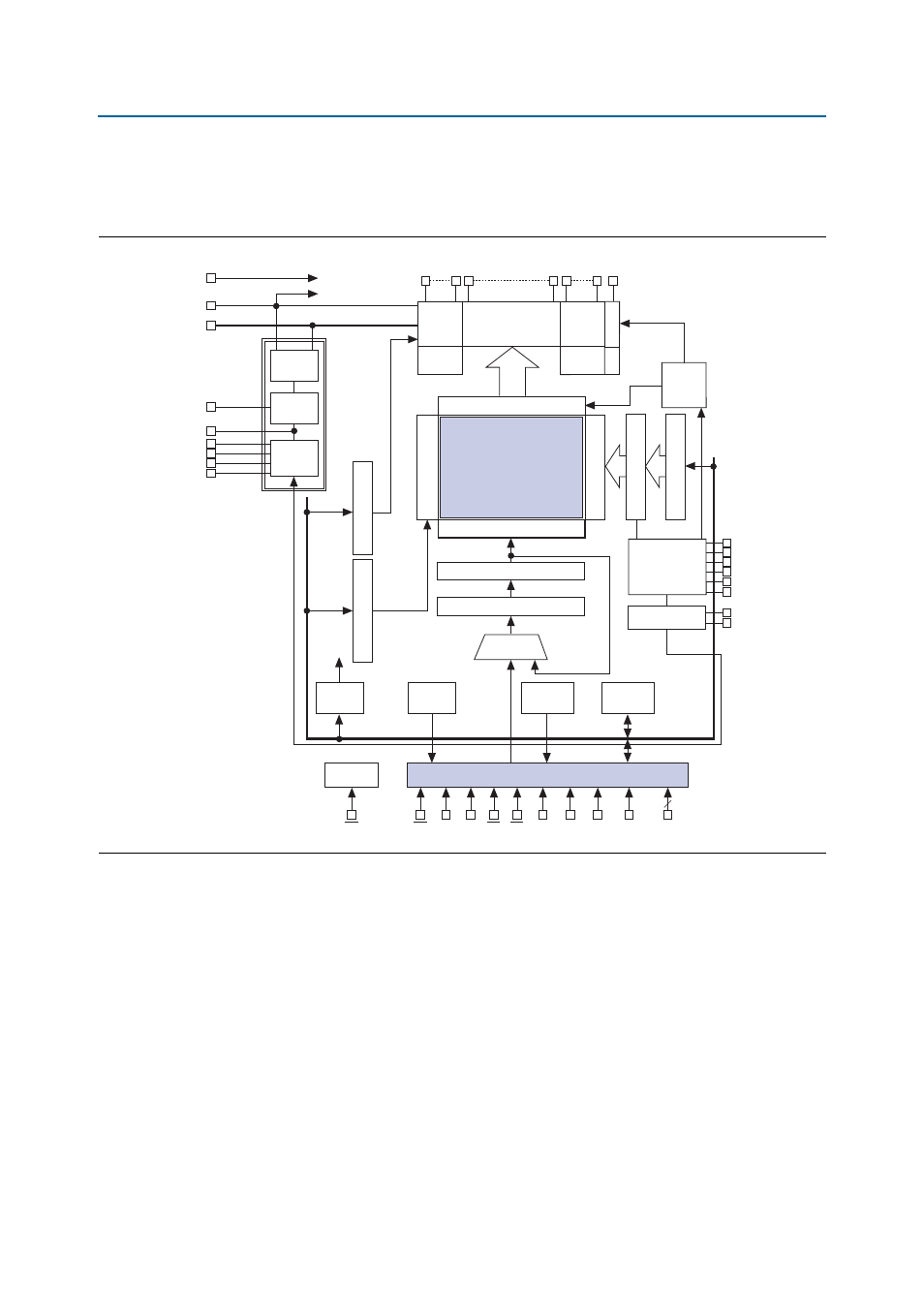

Figure 2–12. Graphics LCD Functional Block Diagram of Display Driver

Segment Drivers

Common

Drivers

Shift

Register

Shift

Register

Common

Drivers

Display Data RAM

65 X 132 = 8,580-bit

Display Data Latch

Low Address Deocder

Line Address Deocder

Column Address Decoder

Vss

VDD

Oscillator

Bus Holder

Busy Flag

Instruction

Decoder

Status

Voltage

Followers

Voltage

Regulator

Voltage

Converter

Multiplexer

Line Counter

Initial Displa

y Line

Common Direction

P

age Address Register

Column Address Counter

Column Address Register

MPU Interface

Reset

Common

Timing

Display Timing

VR

C1+/C1-

C2+/C2-

C3-

Vss2

Vout

V1 to V6

Internal

Power

Circuits

C0 - - - C21

C63 - - - C32

MS

S0 - - - S131

FR

FRS

CL

CLS

DOF

OSC1

OSC2

D5 to D0

P/S

D6

(SCL)

D7

(SI)

C86

A0

CS2

CS1

WR

Status

Internal Bus Line

RD

RES

COMM

- MAX 10 JTAG (15 pages)

- MAX 10 Power (21 pages)

- Unique Chip ID (12 pages)

- Remote Update IP Core (43 pages)

- Device-Specific Power Delivery Network (28 pages)

- Device-Specific Power Delivery Network (32 pages)

- Hybrid Memory Cube Controller (69 pages)

- ALTDQ_DQS IP (117 pages)

- MAX 10 Embedded Memory (71 pages)

- MAX 10 Embedded Multipliers (37 pages)

- MAX 10 Clocking and PLL (86 pages)

- MAX 10 FPGA (26 pages)

- MAX 10 FPGA (56 pages)

- USB-Blaster II (22 pages)

- GPIO (22 pages)

- LVDS SERDES (27 pages)

- User Flash Memory (33 pages)

- ALTDQ_DQS2 (100 pages)

- Avalon Tri-State Conduit Components (18 pages)

- Cyclone V Avalon-MM (166 pages)

- Cyclone III FPGA Starter Kit (36 pages)

- Cyclone V Avalon-ST (248 pages)

- Stratix V Avalon-ST (286 pages)

- Stratix V Avalon-ST (293 pages)

- DDR3 SDRAM High-Performance Controller and ALTMEMPHY IP (10 pages)

- Arria 10 Avalon-ST (275 pages)

- Avalon Verification IP Suite (224 pages)

- Avalon Verification IP Suite (178 pages)

- FFT MegaCore Function (50 pages)

- DDR2 SDRAM High-Performance Controllers and ALTMEMPHY IP (140 pages)

- Floating-Point (157 pages)

- Integer Arithmetic IP (157 pages)

- Embedded Peripherals IP (336 pages)

- JESD204B IP (158 pages)

- Low Latency Ethernet 10G MAC (109 pages)

- LVDS SERDES Transmitter / Receiver (72 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (3 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (80 pages)

- IP Compiler for PCI Express (372 pages)

- Parallel Flash Loader IP (57 pages)

- Nios II C2H Compiler (138 pages)

- RAM-Based Shift Register (26 pages)

- RAM Initializer (36 pages)

- Phase-Locked Loop Reconfiguration IP Core (51 pages)

- DCFIFO (28 pages)