Altera Stratix III Development Board User Manual

Page 24

2–16

Chapter 2: Board Components

MAX II CPLD

Stratix III 3SL150 Development Board

May 2013

Altera Corporation

Reference Manual

lists the MAX II component reference and manufacturing information.

G15

JTAG output from HSMC A

HSMA_JTAG_TDO

1.8 V

—

J18 pin 37

F15

JTAG output from HSMC B

HSMB_JTAG_TDO

1.8 V

—

J8 pin 37

F16

HSMC A present

HSMA_PSNTn

1.8 V

—

J18 pin 160

G13

HSMC B present

HSMB_PSNTn

1.8 V

—

J8 pin 160

G14

JTAG control signal

FPGA_BYPASS

1.8 V

—

SW1 pin 8

E16

JTAG control signal

HSMA_BYPASS

1.8 V

—

SW1 pin 7

F11

JTAG control signal

HSMB_BYPASS

1.8 V

—

SW1 pin 6

C14

JTAG control signal

JTAG_SEL

1.8 V

—

U3 pin 1 and J3 pin 1

M9

MAX II reset

CPU_RESETn

1.8 V

AP5

S6

M8

MAX II enable

MAX_EN

1.8 V

—

SW1 pin 5

H15

MAX II status signal

MAX_ERROR

1.8 V

—

D34

H14

MAX II status signal

MAX_LOAD

1.8 V

—

D33

G16

MAX II status signal

MAX_FACTORY

1.8 V

—

D36

G12

MAX II status signal

MAX_USER

1.8 V

—

D35

E15

MAX II status signal

MAX_EMB

1.8 V

—

D1

E13

MAX II status signal

DEV_SEL

1.8 V

—

U2 pin 1 and J2 pin 1

E14

Control signal

MWATTS_MAMPS

1.8 V

—

SW2 pin 1

D13

Control signal

VOLTS_WATTS

1.8 V

—

SW2 pin 2

R16

Control signal

RESET_CONFIGn

1.8 V

—

S7

N14

PFL enable

MAX_DIP0

1.8 V

—

SW2 pin 5

M13

N/A

MAX_DIP1

1.8 V

—

SW2 pin 6

N15

N/A

MAX_DIP2

1.8 V

—

SW2 pin 7

L14

N/A

MAX_DIP3

1.8 V

—

SW2 pin 8

K16

N/A

MAX_RESERVE0

1.8 V

—

SW2 pin 3

J15

N/A

MAX_RESERVE1

1.8 V

—

SW2 pin 4

E7

N/A

OVERTEMPn

2.5 V

—

J7 pin 2

N1

N/A

TSENSE_SMB_DATA

2.5 V

—

U16 pin 7

L3

N/A

TSENSE_SMB_CLK

2.5 V

—

U16 pin 6

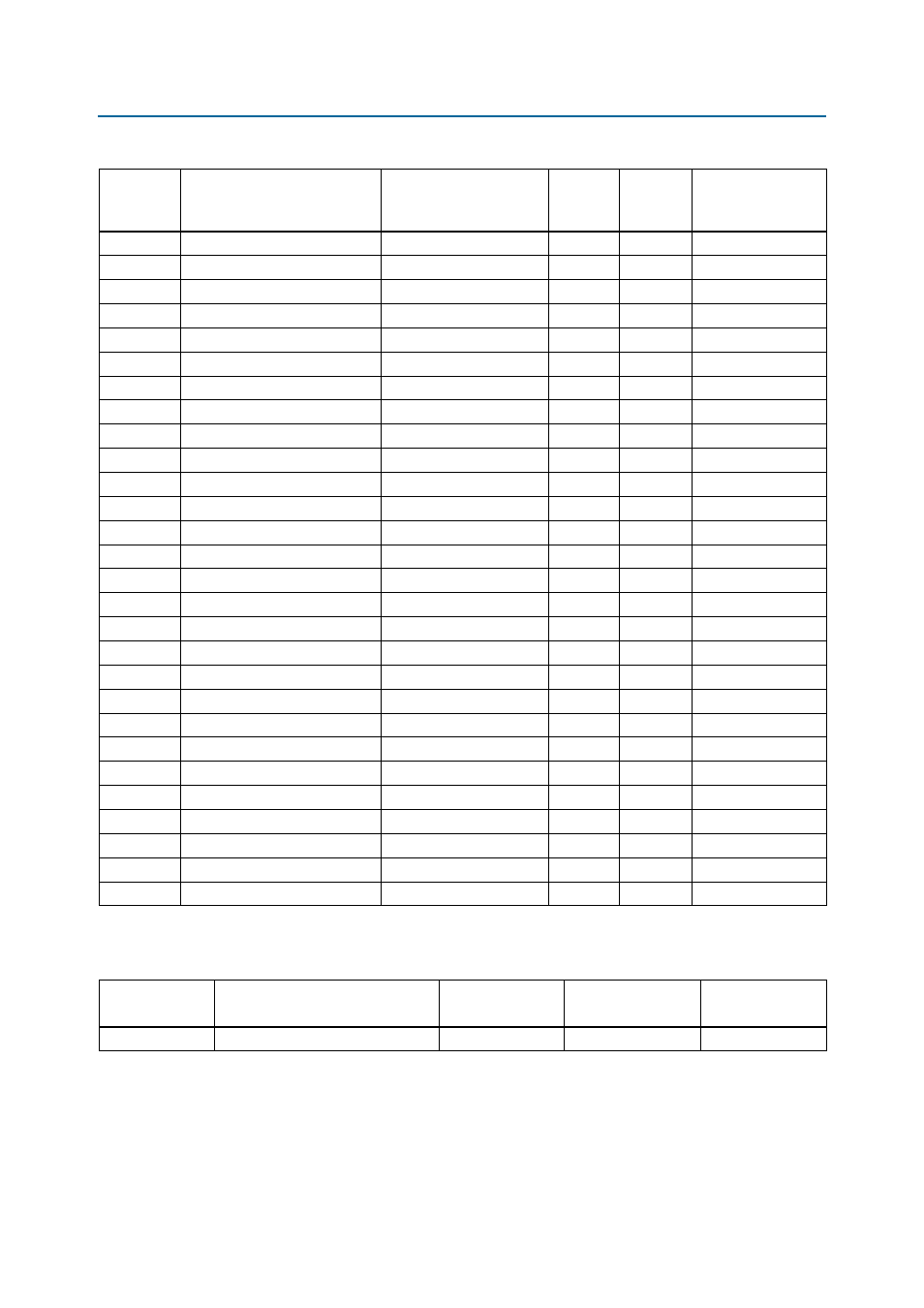

Table 2–5. MAX II Device Pin-out (Part 9 of 9)

MAX II

Pin Number

Description

Schematic Signal Name

I/O

Standard

Stratix III

Pin

Number

Other Connections

Table 2–6. MAX II Component Reference and Manufacturing Information

Board Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

U5

256-pin device in a BGA package

Altera Corporation

EPM2210GF256C3N