Stratix iii fpga clock inputs, Stratix iii fpga clock inputs –26 – Altera Stratix III Development Board User Manual

Page 34

2–26

Chapter 2: Board Components

Clocking Circuitry

Stratix III 3SL150 Development Board

May 2013

Altera Corporation

Reference Manual

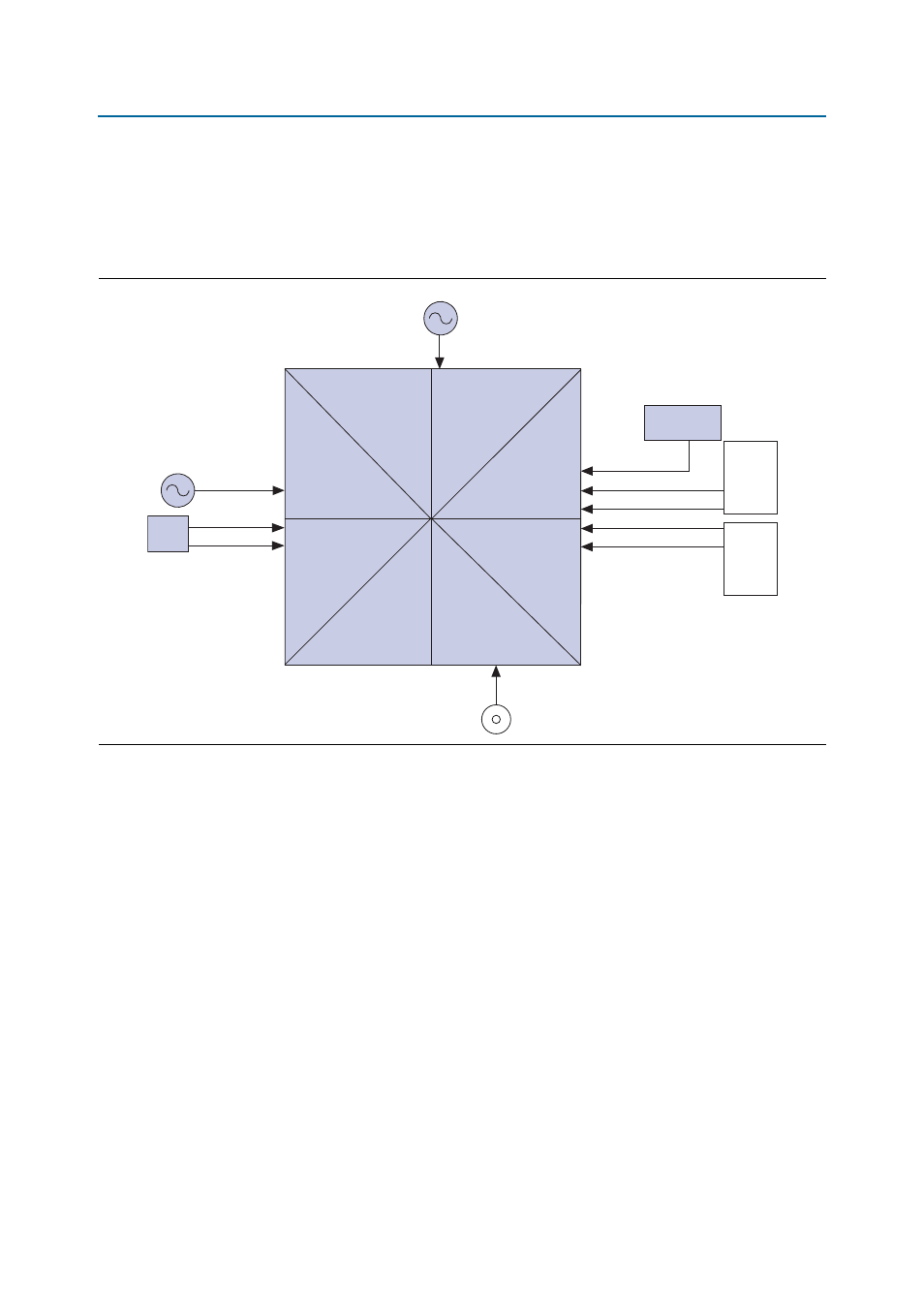

Stratix III FPGA Clock Inputs

outlines the inputs from the Stratix III FPGA. All PLL inputs are located in

the C sub-bank of each device bank. The clocks are sourced by the on-board

oscillators, SMA connectors, Ethernet, MAX II CPLD, and HSMC ports.

Figure 2–7. Stratix III FPGA Clock Inputs

Bank 8C

1.8 V

CLK14N

CLKIN_125

CLK14P

CLK15N

CLK15P

CLK12N

CLK12P

CLK13N

CLK13P

CLK5N

CLK5P

CLK4N

CLK4P

CLK7N

CLK7P

CLK6N

CLK6P

CLK1N

CLK1P

USB_IFCLK

500 MHz

CLK0N

CLK0P

CLK3N

CLK3P

CLK2N

CLK2P

ENET_S_CLKP

ENET_S_CLKN

CLK11N

CLK11P

CLK10N

CLK10P

CLK8N

CLK8P

CLK9N

CLK9P

Bank 7C

1.5 V

Bank 3C

1.8 V

Bank 4C

1.8 V

Bank 6C

2.5 V

Bank 5C

2.5 V

Bank 1C

1.8 V

Bank 2C

2.5 V

HSMA_CLK_IN_P2

HSMA_CLK_IN_N2

HSMB_CLK_IN_P2

HSMB_CLK_IN_N2

CLKIN_SMA

500 MHz

ENET

PHY

MAX II Device

HSMC

Port A

HSMC

Port B

SMA Input

- MAX 10 JTAG (15 pages)

- MAX 10 Power (21 pages)

- Unique Chip ID (12 pages)

- Remote Update IP Core (43 pages)

- Device-Specific Power Delivery Network (28 pages)

- Device-Specific Power Delivery Network (32 pages)

- Hybrid Memory Cube Controller (69 pages)

- ALTDQ_DQS IP (117 pages)

- MAX 10 Embedded Memory (71 pages)

- MAX 10 Embedded Multipliers (37 pages)

- MAX 10 Clocking and PLL (86 pages)

- MAX 10 FPGA (26 pages)

- MAX 10 FPGA (56 pages)

- USB-Blaster II (22 pages)

- GPIO (22 pages)

- LVDS SERDES (27 pages)

- User Flash Memory (33 pages)

- ALTDQ_DQS2 (100 pages)

- Avalon Tri-State Conduit Components (18 pages)

- Cyclone V Avalon-MM (166 pages)

- Cyclone III FPGA Starter Kit (36 pages)

- Cyclone V Avalon-ST (248 pages)

- Stratix V Avalon-ST (286 pages)

- Stratix V Avalon-ST (293 pages)

- DDR3 SDRAM High-Performance Controller and ALTMEMPHY IP (10 pages)

- Arria 10 Avalon-ST (275 pages)

- Avalon Verification IP Suite (224 pages)

- Avalon Verification IP Suite (178 pages)

- FFT MegaCore Function (50 pages)

- DDR2 SDRAM High-Performance Controllers and ALTMEMPHY IP (140 pages)

- Floating-Point (157 pages)

- Integer Arithmetic IP (157 pages)

- Embedded Peripherals IP (336 pages)

- JESD204B IP (158 pages)

- Low Latency Ethernet 10G MAC (109 pages)

- LVDS SERDES Transmitter / Receiver (72 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (3 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (80 pages)

- IP Compiler for PCI Express (372 pages)

- Parallel Flash Loader IP (57 pages)

- Nios II C2H Compiler (138 pages)

- RAM-Based Shift Register (26 pages)

- RAM Initializer (36 pages)

- Phase-Locked Loop Reconfiguration IP Core (51 pages)

- DCFIFO (28 pages)