Power display, Setup elements, Jtag control dip switch – Altera Stratix III Development Board User Manual

Page 29: Power display –21, Setup elements –21, Jtag control dip switch –21, R to

Chapter 2: Board Components

2–21

Configuration, Status, and Setup Elements

May 2013

Altera Corporation

Stratix III 3SL150 Development Board

Reference Manual

lists the board-specific LEDs component reference and manufacturing

information.

Power Display

The power being measured by the MAX II CPLD and associated A/D is displayed on

a dedicated 7-segment display connected to the MAX II device called Power Display.

Setup Elements

The development board includes user, JTAG control, and board-specific DIP switches;

system reset and configuration push-button switches; and rotary switches. This

section discusses the following items:

■

JTAG control DIP switch

■

MAX II device control DIP switch

■

System reset and configuration push-buttons

■

Power Select rotary switch

■

PGM Config Select rotary switch

JTAG Control DIP Switch

Board reference SW1 is a four-position JTAG control DIP switch, provided to either

remove or include devices in the active JTAG chain. Additionally, the JTAG control

DIP switch is also used to disable the embedded USB-Blaster cable when using an

external USB-Blaster cable.

lists the switch position, name, and

description.

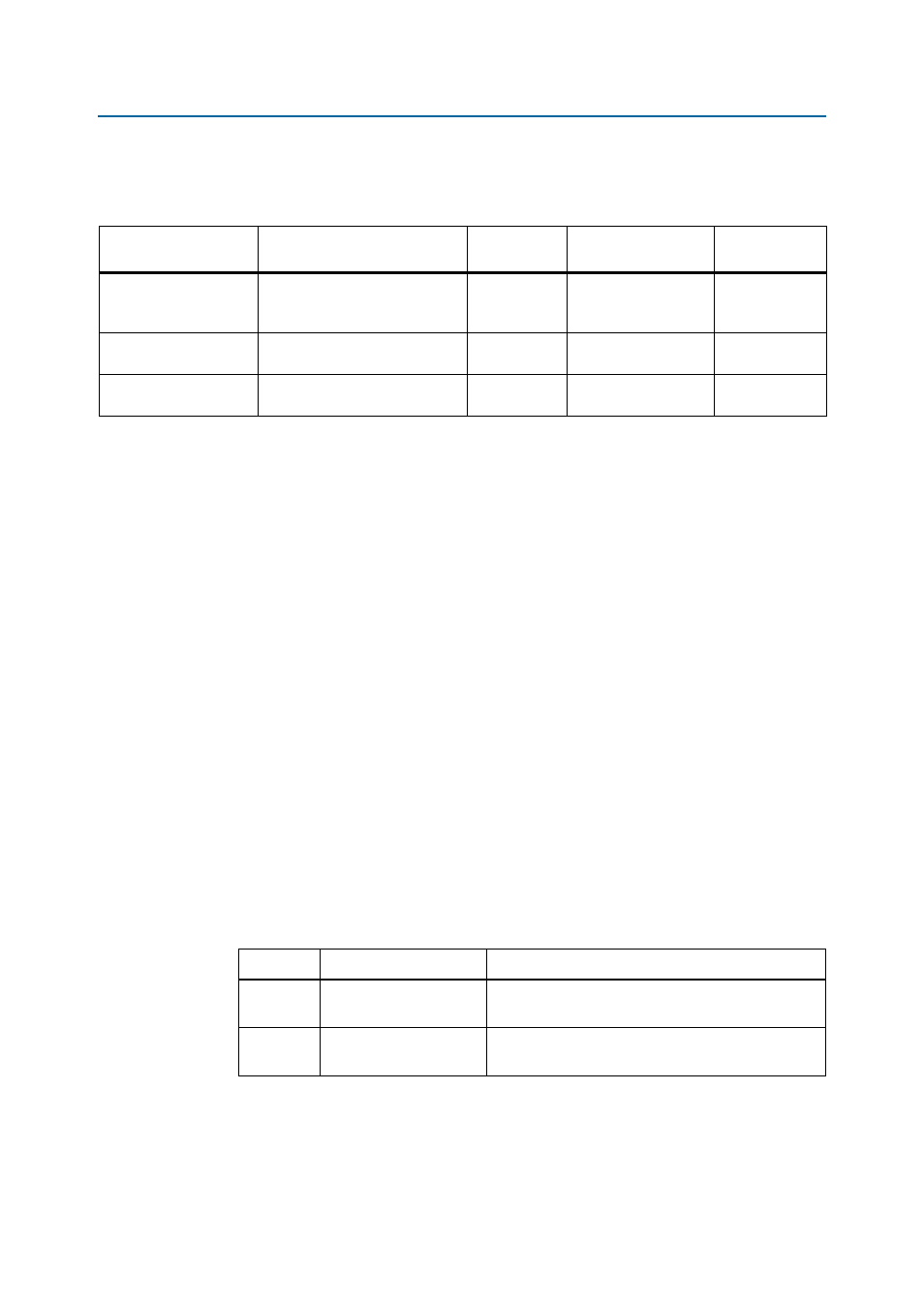

Table 2–9. Board-Specific LEDs Component Reference and Manufacturing Information

Board Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

D2, D3, D6 – D12, D14,

D15, D17, D32, D33,

D35, D36

Green LED, 1206, SMT, clear lens,

2.1 V

Lumex, Inc.

SML-LX1206GC-TR

D16

Blue LED, 1206, SMT, clear lens,

3.5 V

Lumex, Inc.

SML-LX1206USBC-TR

D34

Red LED, 1206, SMT, clear lens,

2.0 V

Lumex, Inc.

SML-LX1206IC-TR

Table 2–10. JTAG Control DIP Switch Signal Names and Descriptions (Part 1 of 2)

DIP Switch

Signal Name

Description

1

FPGA_BYPASS

1 = FPGA in JTAG chain

0 = FPGA not in JTAG chain

2

HSMA_BYPASS

1 = HSMC Port A in JTAG chain (only if installed)

0 = HSMC Port A not in JTAG chain