Altera Stratix III Development Board User Manual

Page 23

Chapter 2: Board Components

2–15

MAX II CPLD

May 2013

Altera Corporation

Stratix III 3SL150 Development Board

Reference Manual

H16

Power selection input

PWR_SEL2

1.8 V

—

SW6 pin P4

H13

Power selection input

PWR_SEL3

1.8 V

—

SW6 pin P8

M4

JTAG master data input signal

FPGA_JTAG_TDI

2.5 V

G28

U2 pin 13

N2

JTAG master data output

FPGA_JTAG_TDO

2.5 V

G29

U2 pin 10

L16

MAX II chip select

MAX_CSn

1.8 V

C20

—

P3

JTAG clock

MAX_JTAG_TCK

2.5 V

F30

U3 pin 2 and U2 pin

2

N4

JTAG mode select

MAX_JTAG_TMS

2.5 V

—

U3 pin 5, U2 pin 5

K15

MAX II write enable

MAX_WEn

1.8 V

G21

—

K13

MAX II output enable

MAX_OEn

1.8 V

D20

—

H1

Connected to Stratix III device

MAX_TO_STRATIX3

2.5 V

K1

—

G4

N/A

MAXGP_JTAG_TCK

2.5 V

—

U3 pin 3

G1

N/A

MAXGP_JTAG_TDI

2.5 V

—

U3 pin 13

G5

N/A

MAXGP_JTAG_TDO

2.5 V

—

U3 pin 10

H2

N/A

MAXGP_JTAG_TMS

2.5 V

—

U3 pin 6

J4

Synchronous clock for

switching regulators

LT4601_CLK0

2.5 V

—

U32 pin A8

K1

Synchronous clock for

switching regulators

LT4601_CLK90

2.5 V

—

U33 pin A8

J3

Synchronous clock for

switching regulators

LT4601_CLK180

2.5 V

—

U34 pin A8

N3

JTAG clock

FPGA_JTAG_TCK

2.5 V

F30

J18 pin 35 and J8

pin 35 and U2 pin 3

P2

JTAG mode select

FPGA_JTAG_TMS

2.5 V

H28

J18 pin 36 and J8

pin 36 and U2 pin 6

L6

JTAG data input

MAX_JTAG_TDI

2.5 V

—

U3 pin 14 and U2

pin 14

M5

JTAG data output

MAX_JTAG_TDO

2.5 V

—

U3 pin 11 and U2

pin 11

A10

Push-button that re-loads the

factory default image into the

Stratix III device

FACTORY_CONFIGn

2.5 V

—

S1

B9

JTAG input to HSMC B

HSMB_JTAG_TDI

2.5 V

—

J8 pin 38

D9

JTAG input to HSMC A

HSMA_JTAG_TDI

2.5 V

—

J18 pin 38

C8

FTDI USB read enable

USB_RDn

2.5 V

—

U11 pin 16

A6

FTDI USB write enable

USB_WR

2.5 V

—

U11 pin 15

A5

FTDI USB reset

USB_RSTn

2.5 V

—

U11 pin 4

D7

FTDI USB reset output

USB_RSTOUTn

2.5 V

—

U11 pin 5

K12

FTDI USB power enable

USB_PWR_ENn

1.8 V

—

U11 pin 10

J12

24 MHz clock input

CLKIN_24

1.8 V

—

Y4 pin 3

H12

125 MHz clock input

CLKIN_MAX_125

1.8 V

—

Y1 pin 4

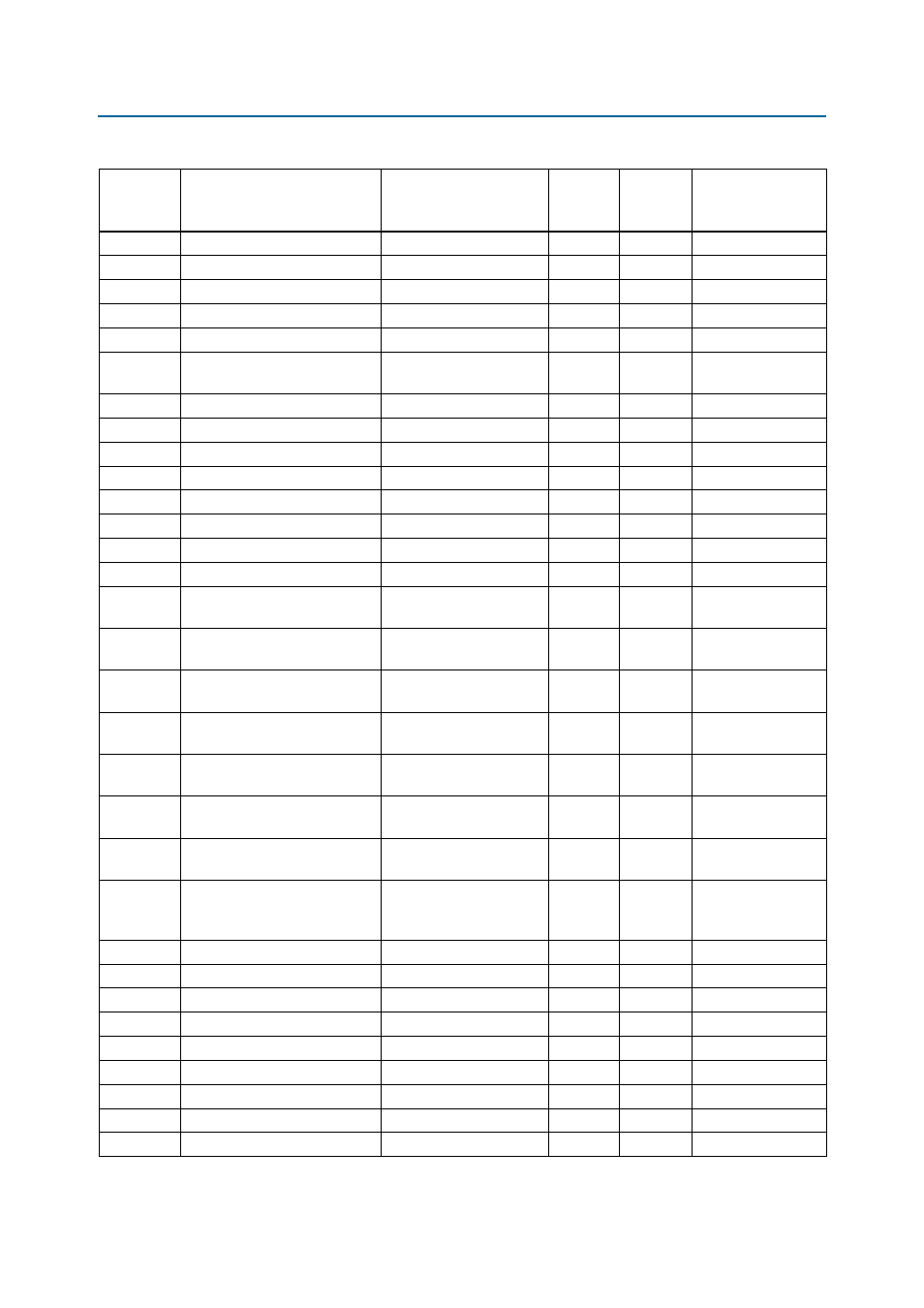

Table 2–5. MAX II Device Pin-out (Part 8 of 9)

MAX II

Pin Number

Description

Schematic Signal Name

I/O

Standard

Stratix III

Pin

Number

Other Connections