Altera Stratix III Development Board User Manual

Page 60

2–52

Chapter 2: Board Components

On-Board Memory

Stratix III 3SL150 Development Board

May 2013

Altera Corporation

Reference Manual

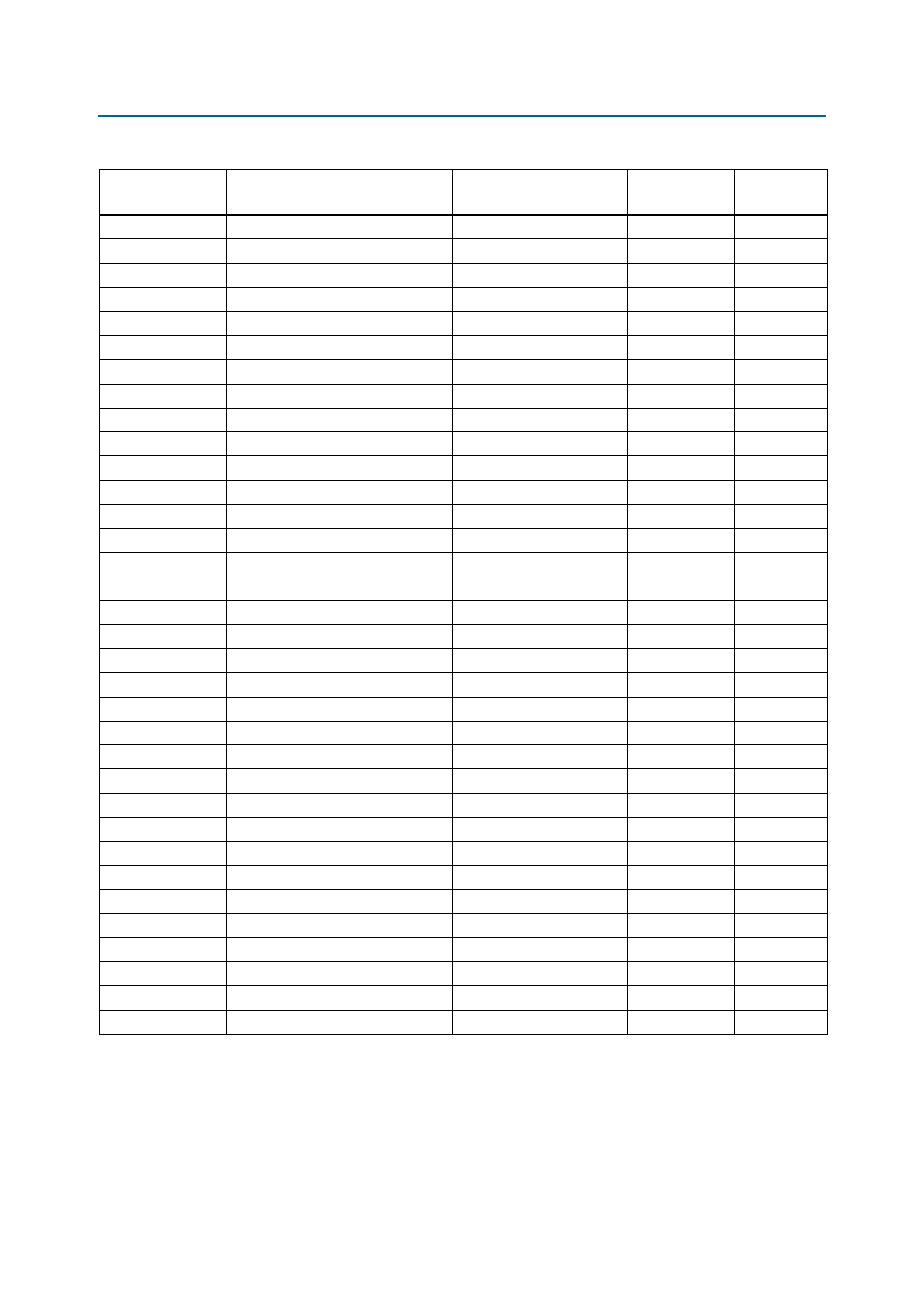

J19 pin 27

Data strobe bit 2

DDR2_DIMM_DQS_N2

SSTL-18 class I

AJ14

J19 pin 36

Data strobe bit 3

DDR2_DIMM_DQS_N3

SSTL-18 class I

AP22

J19 pin 83

Data strobe bit 4

DDR2_DIMM_DQS_N4

SSTL-18 class I

AP25

J19 pin 92

Data strobe bit 5

DDR2_DIMM_DQS_N5

SSTL-18 class I

AP28

J19 pin 104

Data strobe bit 6

DDR2_DIMM_DQS_N6

SSTL-18 class I

AM32

J19 pin 113

Data strobe bit 7

DDR2_DIMM_DQS_N7

SSTL-18 class I

AP33

J19 pin 45

Data strobe bit 8

DDR2_DIMM_DQS_N8

SSTL-18 class I

AM24

J19 pin 7

Data strobe bit 0

DDR2_DIMM_DQS_P0

SSTL-18 class I

AL10

J19 pin 16

Data strobe bit 1

DDR2_DIMM_DQS_P1

SSTL-18 class I

AM9

J19 pin 28

Data strobe bit 2

DDR2_DIMM_DQS_P2

SSTL-18 class I

AH14

J19 pin 37

Data strobe bit 3

DDR2_DIMM_DQS_P3

SSTL-18 class I

AN22

J19 pin 84

Data strobe bit 4

DDR2_DIMM_DQS_P4

SSTL-18 class I

AN25

J19 pin 93

Data strobe bit 5

DDR2_DIMM_DQS_P5

SSTL-18 class I

AN28

J19 pin 105

Data strobe bit 6

DDR2_DIMM_DQS_P6

SSTL-18 class I

AM31

J19 pin 114

Data strobe bit 7

DDR2_DIMM_DQS_P7

SSTL-18 class I

AN33

J19 pin 46

Data strobe bit 8

DDR2_DIMM_DQS_P8

SSTL-18 class I

AL24

J19 pin 195

On-die termination control bit 0

DDR2_DIMM_ODT0

SSTL-18 class I

AE19

J19 pin 77

On-die termination control bit 1

DDR2_DIMM_ODT1

SSTL-18 class I

AD19

J19 pin 52

Clock enable bit 0

DDR2_DIMM_CKE0

SSTL-18 class I

AJ16

J19 pin 171

Clock enable bit 1

DDR2_DIMM_CKE1

SSTL-18 class I

AP7

J19 pin 186

Differential output clock 0

DDR2_DIMM_CLK_N0

SSTL-18 class I

AM14

J19 pin 138

Differential output clock 1

DDR2_DIMM_CLK_N1

SSTL-18 class I

AL13

J19 pin 221

Differential output clock 2

DDR2_DIMM_CLK_N2

SSTL-18 class I

AM15

J19 pin 185

Differential output clock 0

DDR2_DIMM_CLK_P0

SSTL-18 class I

AL14

J19 pin 137

Differential output clock 1

DDR2_DIMM_CLK_P1

SSTL-18 class I

AK13

J19 pin 220

Differential output clock 2

DDR2_DIMM_CLK_P2

SSTL-18 class I

AL15

J19 pin 193

Chip select

DDR2_DIMM_CSn0

SSTL-18 class I

AG21

J19 pin 76

Chip select

DDR2_DIMM_CSn1

SSTL-18 class I

AC22

J19 pin 74

Column address strobe

DDR2_DIMM_CASn

SSTL-18 class I

AD18

J19 pin 192

Row address strobe

DDR2_DIMM_RASn

SSTL-18 class I

AN19

J19 pin 18

Reset

DDR2_DIMM_RESETn

SSTL-18 class I

AE18

J19 pin 120

Presence-detect clock

DDR2_DIMM_SCL

SSTL-18 class I

AN15

J19 pin 119

Presence-detect data

DDR2_DIMM_SDA

SSTL-18 class I

AK19

J19 pin 73

Write enable

DDR2_DIMM_WEn

SSTL-18 class I

AJ19

Table 2–45. DDR2 DIMM Interface I/O Signals (Part 4 of 4)

Board Reference

Description

Schematic

Signal Name

I/O Standard

Stratix III

Pin Number