Altera Stratix III Development Board User Manual

Page 53

Chapter 2: Board Components

2–45

Components and Interfaces

May 2013

Altera Corporation

Stratix III 3SL150 Development Board

Reference Manual

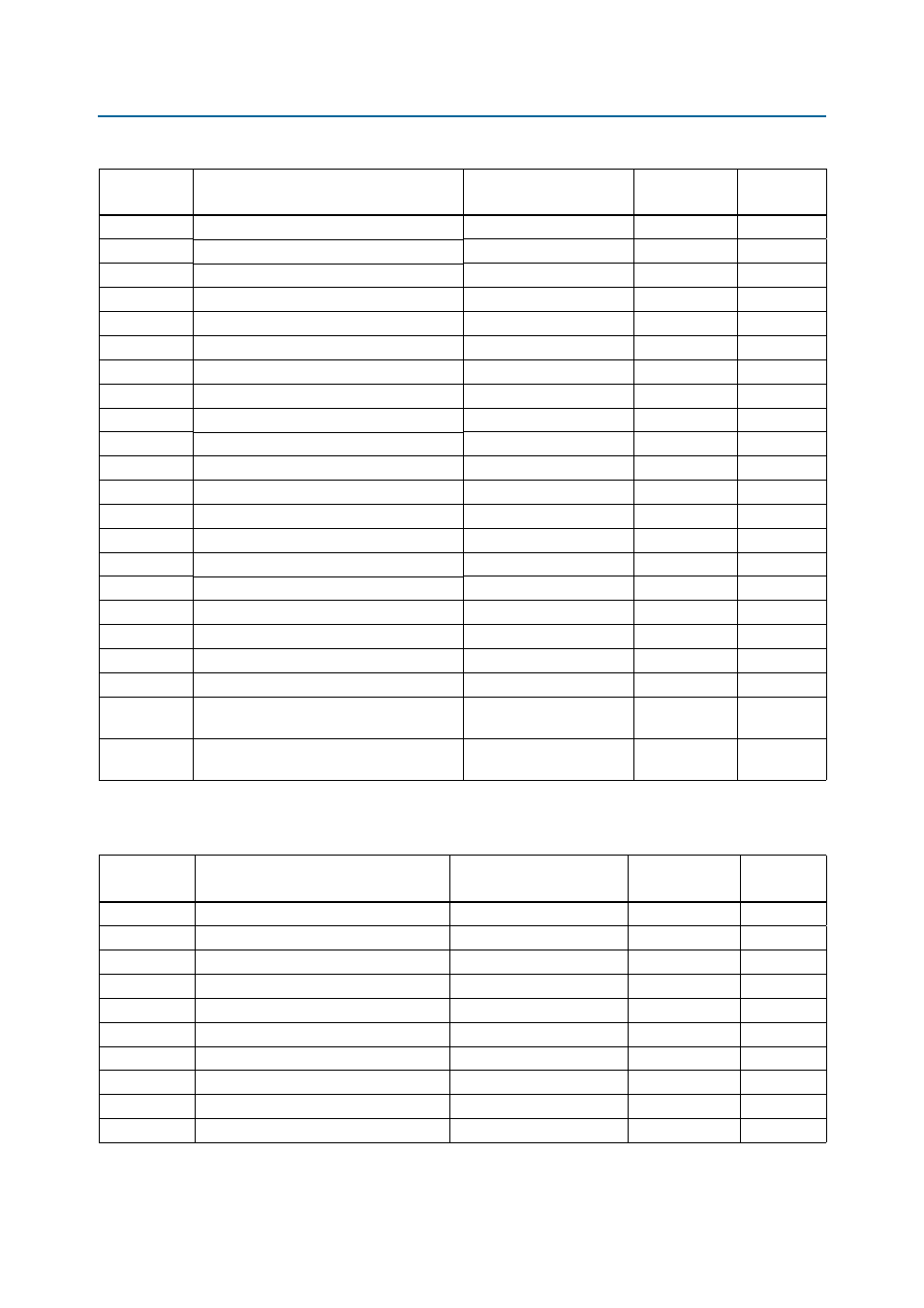

lists the HSMC Port B interface signal name, description, and signal type.

J18 pin 131

LVDS TX or CMOS I/O bit 13

HSMA_TX_P13

LVDS or 2.5 V

Y8

J18 pin 132

LVDS RX or CMOS I/O bit 13

HSMA_RX_P13

LVDS or 2.5 V

AA1

J18 pin 133

LVDS TX or CMOS I/O bit 13

HSMA_TX_N13

LVDS or 2.5 V

Y7

J18 pin 134

LVDS RX or CMOS I/O bit 13

HSMA_RX_N13

LVDS or 2.5 V

AB1

J18 pin 137

LVDS TX or CMOS I/O bit 14

HSMA_TX_P14

LVDS or 2.5 V

Y10

J18 pin 138

LVDS RX or CMOS I/O bit 14

HSMA_RX_P14

LVDS or 2.5 V

AC4

J18 pin 139

LVDS TX or CMOS I/O bit 14

HSMA_TX_N14

LVDS or 2.5 V

Y9

J18 pin 140

LVDS RX or CMOS I/O bit 14

HSMA_RX_N14

LVDS or 2.5 V

AB3

J18 pin 143

LVDS TX or CMOS I/O bit 15

HSMA_TX_P15

LVDS or 2.5 V

W12

J18 pin 144

LVDS RX or CMOS I/O bit 15

HSMA_RX_P15

LVDS or 2.5 V

AB4

J18 pin 145

LVDS TX or CMOS I/O bit 15

HSMA_TX_N15

LVDS or 2.5 V

Y11

J18 pin 146

LVDS RX or CMOS I/O bit 15

HSMA_RX_N15

LVDS or 2.5 V

AA3

J18 pin 149

LVDS TX or CMOS I/O bit 16

HSMA_TX_P16

LVDS or 2.5 V

AA12

J18 pin 150

LVDS RX or CMOS I/O bit 16

HSMA_RX_P16

LVDS or 2.5 V

AA4

J18 pin 151

LVDS TX or CMOS I/O bit 16

HSMA_TX_N16

LVDS or 2.5 V

AB11

J18 pin 152

LVDS RX or CMOS I/O bit 16

HSMA_RX_N16

LVDS or 2.5 V

Y3

J18 pin 155

LVDS or CMOS clock out

HSMA_CLK_OUT_P2

LVDS

W8

J18 pin 156

LVDS or CMOS clock in

HSMA_CLK_IN_P2

LVDS

T2

J18 pin 157

LVDS or CMOS clock out

HSMA_CLK_OUT_N2

2.5 V

W7

J18 pin 158

LVDS or CMOS clock in

HSMA_CLK_IN_N2

2.5 V

T1

N/A

User LED intended to show RX data activity

on the HSMC interface

HSMA_RX_LED

2.5 V

Y25

N/A

User LED intended to show TX data activity

on the HSMC interface

HSMA_TX_LED

2.5 V

AG29

Table 2–41. HSMC Port A Interface Signal Name, Description, and Type (Part 3 of 3)

Board

Reference

Description

Schematic

Signal Name

I/O

Standard

Stratix III

Pin Number

Table 2–42. HSMC Port B Interface Signal Name, Description, and Type (Part 1 of 4)

Board

Reference

Description

Schematic

Signal Name

I/O Standard

Stratix III

Pin Number

J8 pin 33

Serial data

HSMB_SDA

2.5 V

U11

J8 pin 34

Serial clock

HSMB_SCL

2.5 V

AD31

J8 pin 35

JTAG clock signal

FPGA_JTAG_TCK

2.5 V

F30

J8 pin 36

JTAG mode select signal

FPGA_JTAG_TMS

2.5 V

N/A

J8 pin 37

JTAG data output

HSMB_JTAG_TDO

2.5 V

G28

J8 pin 38

JTAG data input

HSMB_JTAG_TDI

2.5 V

N/A

J8 pin 39

Dedicated CMOS clock out

HSMB_CLK_OUT0

2.5 V

AC34

J8 pin 40

Dedicated CMOS clock in

HSMB_CLK_IN0

2.5 V

V4

J8 pin 41

Dedicated CMOS I/O bit 0

HSMB_D0

2.5 V

AB24

J8 pin 42

Dedicated CMOS I/O bit 1

HSMB_D1

2.5 V

AB25