Altera Stratix III Development Board User Manual

Page 48

2–40

Chapter 2: Board Components

Components and Interfaces

Stratix III 3SL150 Development Board

May 2013

Altera Corporation

Reference Manual

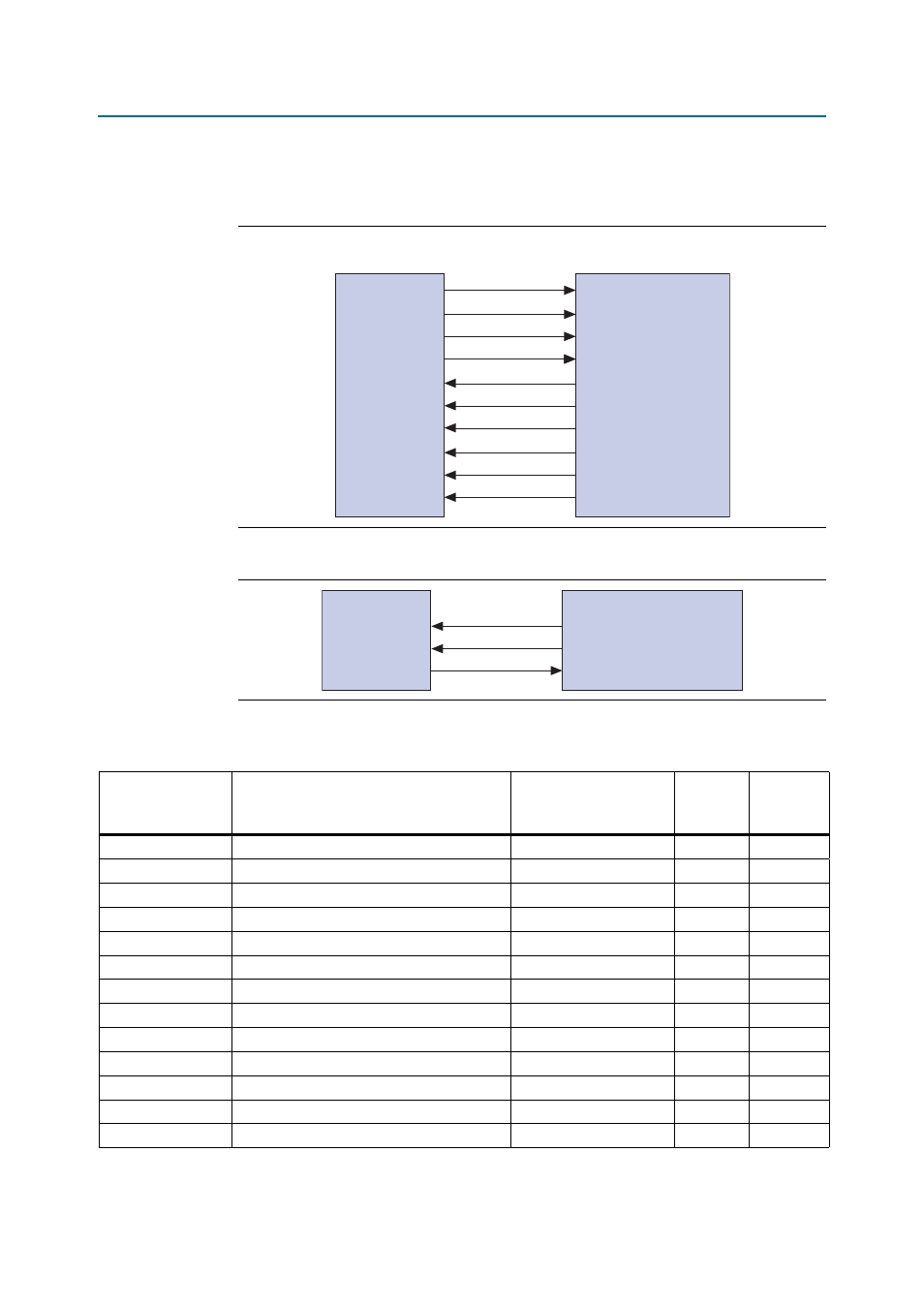

show the GMII and the SGMII interfaces between the

FPGA (MAC) and Marvell PHY 88E1111 device.

lists the pins of the Gigabit Ethernet interface.

Figure 2–14. Marvell 88E1111 GMII Interface

Figure 2–15. Marvell 88E1111 SGMII Interface

GTX_CLK

TX_ER

TX_EN

TXD[7:0]

GTX_CLK

Stratix III Device

MAC Block

Marvell 88E1111

GMII PHY Layer

TX_ER

TX_EN

TXD[7:0]

RX_CLK

RX_ER

RX_DV

RX_CLK

RX_ER

RX_DV

RXD[7:0]

CRS

COL

RXD[7:0]

CRS

COL

GMII Interface

RX

RXCLK

TX

S_OUT+/-

S_CLK +/-

S_IN +/-

Stratix III

Device

MAC Block

Marvell 88E1111

SGMII Interface

PHY Layer

Table 2–39. Ethernet PHY (U25) Pin-Out (Part 1 of 2)

Board Reference

Description

Schematic Signal Name

I/O

Standard

Stratix III

Pin

Number

U25 pin 8

RGMII interface transmit clock

ENET_GTX_CLK

2.5 V

AB33

U25 pin 23

Management bus interrupt

ENET_INTn

2.5 V

AB32

U25 pin 73

1000 MBytes link established

ENET_LED_LINK1000

2.5 V

A28

U25 pin 25

Management bus data clock

ENET_MDC

2.5 V

Y2

U25 pin 24

Management bus data

ENET_MDIO

2.5 V

AD30

U25 pin 28

Reset

ENET_RESETN

2.5 V

Y31

U25 pin 2

RGMII interface receive clock

ENET_RX_CLK

1.8 V

AK28

U25 pin 83

GMII interface collision

ENET_RX_COL

2.5 V

V33

U25 pin 84

GMII interface carrier sense

ENET_RX_CRS

2.5 V

V3

U25 pin 95

GMII/ RGMII interface receive data bus bit 0

ENET_RX_D0

2.5 V

AE29

U25 pin 92

GMII/ RGMII interface receive data bus bit 1

ENET_RX_D1

2.5 V

AM34

U25 pin 93

GMII/ RGMII interface receive data bus bit 2

ENET_RX_D2

2.5 V

AL33

U25 pin 91

GMII/ RGMII interface receive data bus bit 3

ENET_RX_D3

2.5 V

AJ32