Synchronous sram, Synchronous sram –42 – Altera Arria V GX Starter Board User Manual

Page 50

2–42

Chapter 2: Board Components

Memory

Arria V GX Starter Board

November 2013

Altera Corporation

Reference Manual

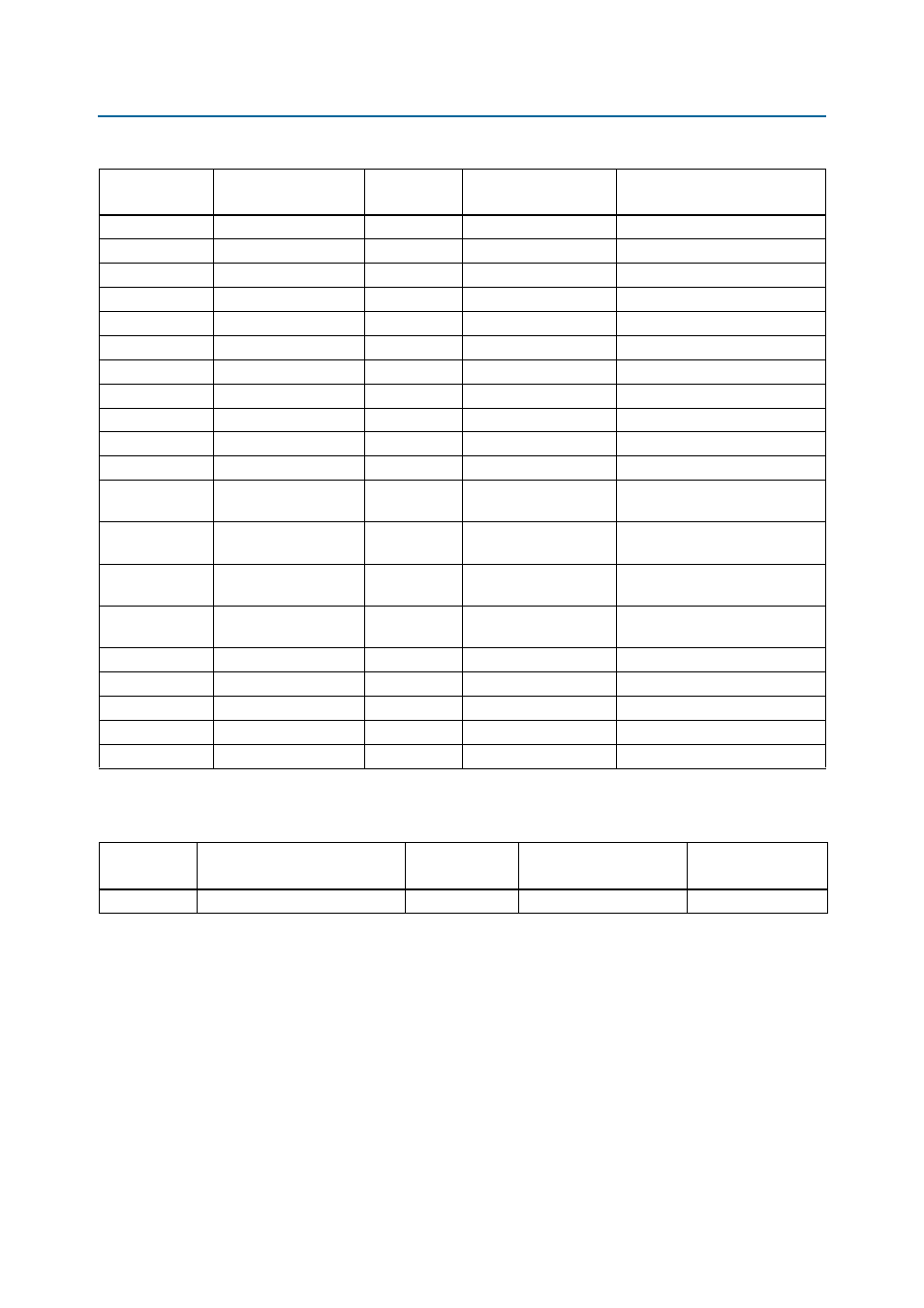

lists the DDR3 component reference and manufacturing information.

Synchronous SRAM

The starter board supports a 18-Mb standard synchronous SRAM intended to be used

by NIOS II systems for instruction and data storage with low-latency random access

capability. The device has a 512K x 36-bits interface (32-bits data and 4-bits parity).

This device is part of the shared FSM bus that connects to the flash memory, SRAM,

and MAX V CPLD 5M2210 System Controller.

The device speed is 200 MHz single-data-rate. There is no minimum speed for this

device. The theoretical bandwidth of this 32-bit interface is 6.4 Gbps for continuous

bursts. The read latency for any address is two clocks while the write latency is one

clock.

H8

DDR3_DQ21

G21

1.5-V SSTL Class I

Data bus byte lane 2

G2

DDR3_DQ22

A23

1.5-V SSTL Class I

Data bus byte lane 2

H7

DDR3_DQ23

B23

1.5-V SSTL Class I

Data bus byte lane 2

D7

DDR3_DQ24

K20

1.5-V SSTL Class I

Data bus byte lane 3

C3

DDR3_DQ25

L20

1.5-V SSTL Class I

Data bus byte lane 3

C8

DDR3_DQ26

M20

1.5-V SSTL Class I

Data bus byte lane 3

C2

DDR3_DQ27

A22

1.5-V SSTL Class I

Data bus byte lane 3

A7

DDR3_DQ28

B21

1.5-V SSTL Class I

Data bus byte lane 3

A2

DDR3_DQ29

B20

1.5-V SSTL Class I

Data bus byte lane 3

B8

DDR3_DQ30

F20

1.5-V SSTL Class I

Data bus byte lane 3

A3

DDR3_DQ31

G20

1.5-V SSTL Class I

Data bus byte lane 3

F3

DDR3_DQS_P2

F22

Differential 1.5-V SSTL

Class I

Data strobe P byte lane 2

G3

DDR3_DQS_N2

G22

Differential 1.5-V SSTL

Class I

Data strobe N byte lane 2

C7

DDR3_DQS_P3

D20

Differential 1.5-V SSTL

Class I

Data strobe P byte lane 3

B7

DDR3_DQS_N3

E20

Differential 1.5-V SSTL

Class I

Data strobe N byte lane 3

K1

DDR3_ODT

H27

1.5-V SSTL Class I

On-die termination enable

J3

DDR3_RASN

B30

1.5-V SSTL Class I

Row address select

T2

DDR3_RESETN

K25

1.5-V SSTL Class I

Reset

L3

DDR3_WEN

F29

1.5-V SSTL Class I

Write enable

L8

DDR3_ZQ2

—

1.5-V SSTL Class I

ZQ impedance calibration

Table 2–43. DDR3 Device Pin Assignments, Schematic Signal Names, and Functions (Part 4 of 4)

Board Reference

Schematic

Signal Name

Arria V GX

Pin Number

I/O Standard

Description

Table 2–44. DDR3 Component Reference and Manufacturing Information

Board

Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

U10, U11

8M×16×8, 1 Gb, DDR3 memory

Micron

MT41J64M16JT-15E