Memory, Ddr3 sdram, Memory –39 – Altera Arria V GX Starter Board User Manual

Page 47: Ddr3 sdram –39

Chapter 2: Board Components

2–39

Memory

November 2013

Altera Corporation

Arria V GX Starter Board

Reference Manual

Memory

This section describes the starter board’s memory interface support and also their

signal names, types, and connectivity relative to the Arria V GX. The starter board has

the following memory interfaces:

■

DDR3 SDRAM

■

Synchronous SRAM

■

Synchronous flash

f

For more information about the memory interfaces, refer to the following documents:

■

section in volume 4 of the External Memory Interface Handbook.

■

section in volume 6 of the

External Memory Interf

DDR3 SDRAM

The starter board supports a 8Mx32x8 bank DDR3 SDRAM interface for very

high-speed sequential memory access. The 32-bit data bus consists of two x16 devices

with a single address or command bus. This interface connects to the vertical I/O

banks on the top edge of the FPGA.

This DDR3 SDRAM has two interface options. The first option is a x32 interface using

a hard memory controller. The second option is a x32 interface using a soft memory

controller.

With a hard memory controller, this interface runs at the target frequency of 533 MHz

for a maximum theoretical bandwidth of 33.31 Gbps. With a soft memory controller,

this interface runs at the target frequency of 667 MHz for a maximum theoretical

bandwidth of 41.66 Gbps. Though a soft memory controller runs at higher data rate

than a hard memory controller, the hard memory controller operates at a much higher

efficiency. The maximum frequency for the Micron device is 667 MHz with a CAS

latency of 9.

lists the DDR3 pin assignments, signal names, and functions. The signal

names and types are relative to the Arria V GX in terms of I/O setting and direction.

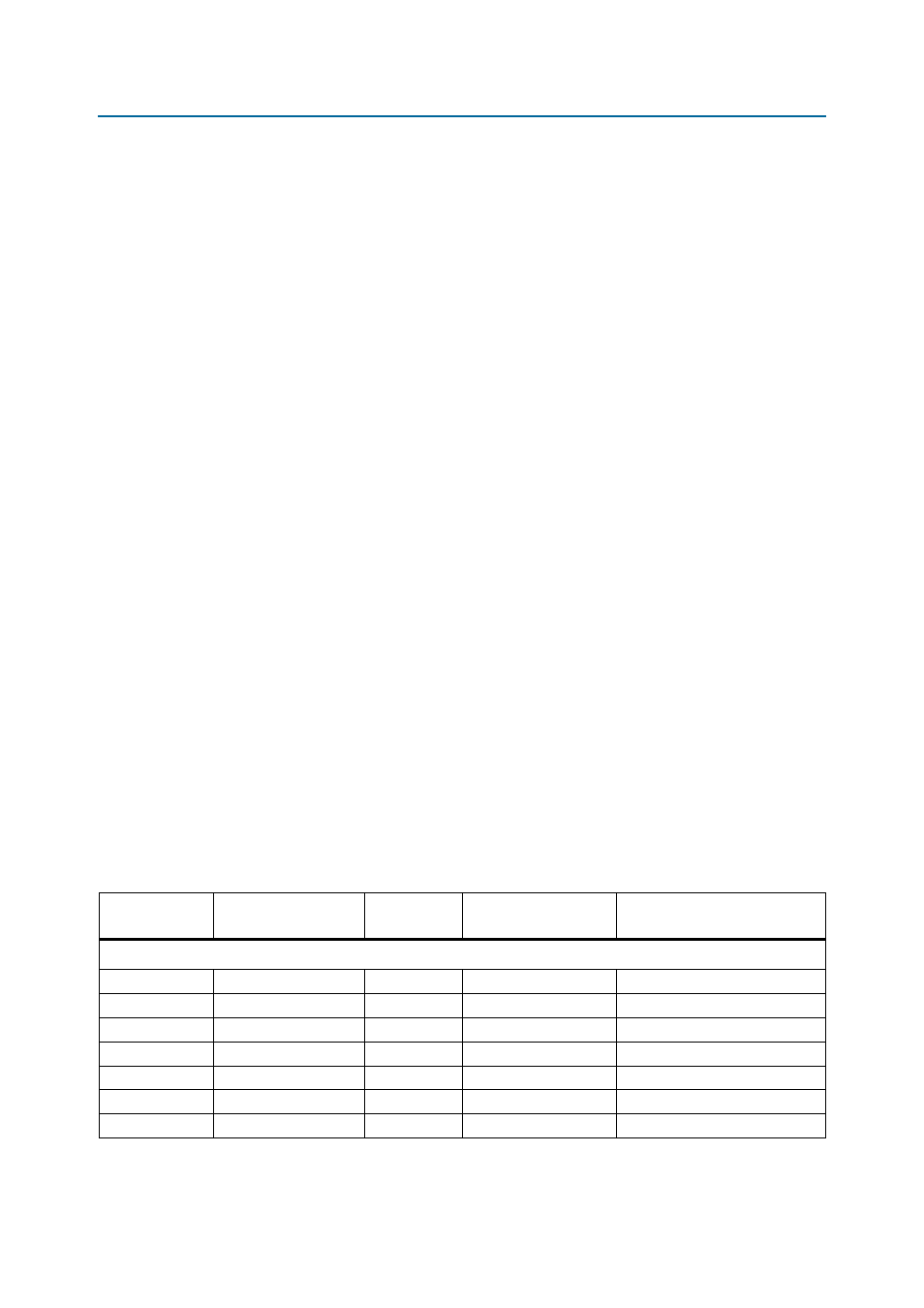

Table 2–43. DDR3 Device Pin Assignments, Schematic Signal Names, and Functions (Part 1 of 4)

Board Reference

Schematic

Signal Name

Arria V GX

Pin Number

I/O Standard

Description

DDR3 x16 (U11)

N3

DDR3_A0

D26

1.5-V SSTL Class I

Address bus

P7

DDR3_A1

E27

1.5-V SSTL Class I

Address bus

P3

DDR3_A2

A27

1.5-V SSTL Class I

Address bus

N2

DDR3_A3

B27

1.5-V SSTL Class I

Address bus

P8

DDR3_A4

G26

1.5-V SSTL Class I

Address bus

P2

DDR3_A5

H26

1.5-V SSTL Class I

Address bus

R8

DDR3_A6

K27

1.5-V SSTL Class I

Address bus