Altera Arria V GX Starter Board User Manual

Page 37

Chapter 2: Board Components

2–29

Components and Interfaces

November 2013

Altera Corporation

Arria V GX Starter Board

Reference Manual

summarizes the PCI Express pin assignments. The signal names and

directions are relative to the Arria V GX.

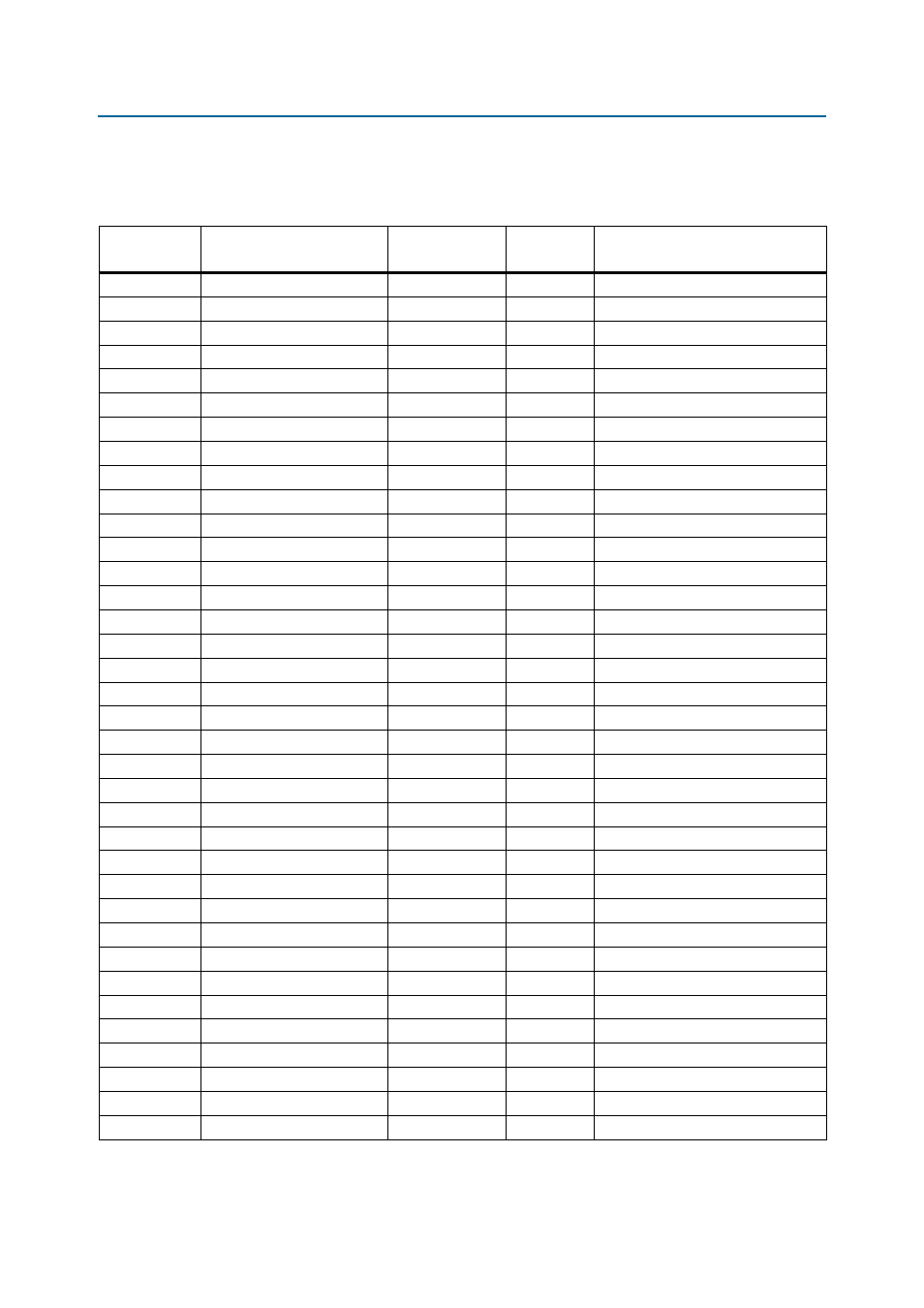

Table 2–31. PCI Express Pin Assignments, Schematic Signal Names, and Functions

Board

Reference (J1)

Schematic Signal Name

Arria V GX

Pin Number

I/O Standard

Description

A5

PCIE_JTAG_TCK

—

LVTTL

JTAG chain clock

A6

PCIE_JTAG_TDI

—

LVTTL

JTAG chain data in

A7

PCIE_JTAG_TDO

—

LVTTL

JTAG chain data out

A8

PCIE_JTAG_TMS

—

LVTTL

JTAG chain mode select

A11

PCIE_PERSTN

B2

LVTTL

Reset

A1

PCIE_PRSNT1N

—

LVTTL

Link width DIP switch

B17

PCIE_PRSNT2N_X1

—

LVTTL

Link width DIP switch

B31

PCIE_PRSNT2N_X4

—

LVTTL

Link width DIP switch

B48

PCIE_PRSNT2N_X8

—

LVTTL

Link width DIP switch

A13

PCIE_REFCLK_P

AA27

HCSL

Motherboard reference clock

A14

PCIE_REFCLK_N

AA28

HCSL

Motherboard reference clock

B14

PCIE_RX_P0

AK34

1.5-V PCML

Receive bus

B15

PCIE_RX_N0

AK33

1.5-V PCML

Receive bus

B19

PCIE_RX_P1

AH34

1.5-V PCML

Receive bus

B20

PCIE_RX_N1

AH33

1.5-V PCML

Receive bus

B23

PCIE_RX_P2

AF34

1.5-V PCML

Receive bus

B24

PCIE_RX_N2

AF33

1.5-V PCML

Receive bus

B27

PCIE_RX_P3

AD34

1.5-V PCML

Receive bus

B28

PCIE_RX_N3

AD33

1.5-V PCML

Receive bus

B33

PCIE_RX_P4

Y34

1.5-V PCML

Receive bus

B34

PCIE_RX_N4

Y33

1.5-V PCML

Receive bus

B37

PCIE_RX_P5

V34

1.5-V PCML

Receive bus

B38

PCIE_RX_N5

V33

1.5-V PCML

Receive bus

B41

PCIE_RX_P6

T34

1.5-V PCML

Receive bus

B42

PCIE_RX_N6

T33

1.5-V PCML

Receive bus

B45

PCIE_RX_P7

P34

1.5-V PCML

Receive bus

B46

PCIE_RX_N7

P33

1.5-V PCML

Receive bus

B5

PCIE_SMBCLK

F16

2.5-V

SMB clock

B6

PCIE_SMBDAT

F14

2.5-V

SMB data

A16

PCIE_TX_CP0

AJ32

1.5-V PCML

Transmit bus

A17

PCIE_TX_CN0

AJ31

1.5-V PCML

Transmit bus

A21

PCIE_TX_CP1

AG32

1.5-V PCML

Transmit bus

A22

PCIE_TX_CN1

AG31

1.5-V PCML

Transmit bus

A25

PCIE_TX_CP2

AE32

1.5-V PCML

Transmit bus

A26

PCIE_TX_CN2

AE31

1.5-V PCML

Transmit bus

A29

PCIE_TX_CP3

AC32

1.5-V PCML

Transmit bus