Pci express, Pci express –28 – Altera Arria V GX Starter Board User Manual

Page 36

2–28

Chapter 2: Board Components

Components and Interfaces

Arria V GX Starter Board

November 2013

Altera Corporation

Reference Manual

PCI Express

The Arria V GX starter board is designed to fit entirely into a PC motherboard with a

×8 PCI Express slot that can accommodate a full height long form factor add-in card.

This interface uses the Arria V GX's PCI Express hard IP block, saving logic resources

for the user logic application.

f

For more information on using the PCI Express hard IP block, refer to

.

The PCI Express edge connector has a connection speed of 2.5 Gbps/lane for a

maximum of 20 Gbps full-duplex (Gen1) or 5.0 Gbps/lane for a maximum of 40 Gbps

full-duplex (Gen2).

The power for the board can be sourced entirely from the PCI Express edge connector

when installed into a PC motherboard. Although the board can also be powered by a

laptop power supply for use on a lab bench, it is not recommended to power from

both supplies at the same time. Ideal diode power sharing devices have been

designed into this board to prevent damages or back-current from one supply to the

other.

The PCIE_REFCLK_P/N signal is a 100 MHz differential input that is driven from the PC

motherboard on to this board through the edge connector. This signal connects

directly to a Arria V GX REFCLK input pin pair using DC coupling. This clock is

terminated on the motherboard and therefore, no on-board termination is required.

This clock can have spread-spectrum properties that change its period between

9.847 ps to 10.203 ps. The I/O standard is High-Speed Current Steering Logic (HCSL).

shows the PCI Express reference clock levels.

The JTAG and SMB are optional signals in the PCI Express specification. Both types of

signals are wired to the Arria V GX but are not required for normal operation. The PCI

Express control DIP switch allows the presence detect grounding to be altered to

enable a ×1, ×4, or ×8 width edge connector. The PCI Express control DIP switch does

not support auto-negotiation.

The PCI express edge connector has a presence detect feature to allow the

motherboard to determine if a card is installed. A DIP switch provides an option to

connect the PRSNT1n pin to any of the three PRSNT2n pins found within the ×8

connector definition. This is to address issues on some PC systems that would base

the link width capability on the presence detect pins versus a query operation.

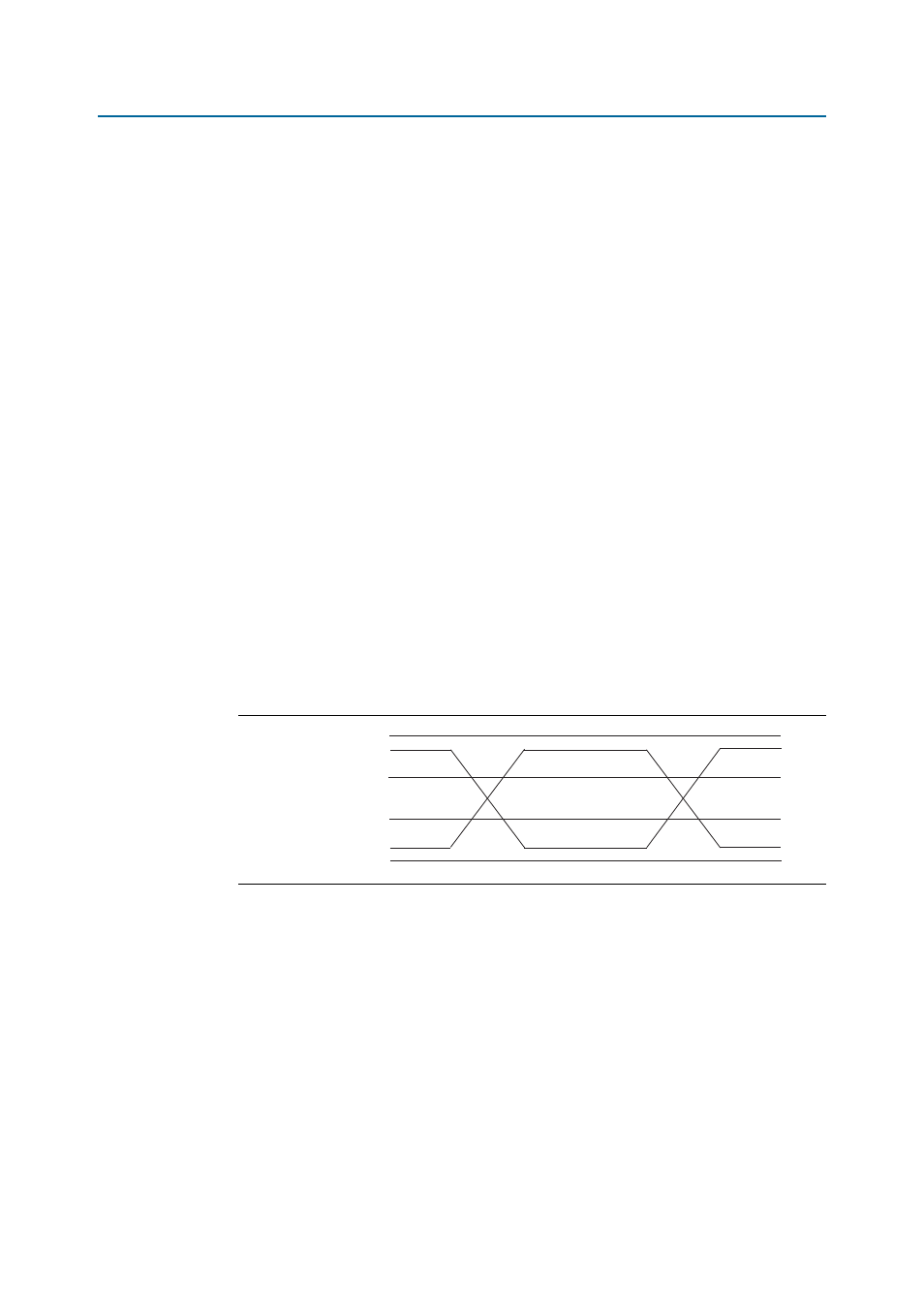

Figure 2–8. PCI Express Reference Clock Levels

V

MAX

= 1.15 V

V

CROSS MAX

= 550 mV

V

CROSS MIN

= 250 mV

V

MIN

= –0.30 V

REFCLK –

REFCLK +