Altera Arria V GX Starter Board User Manual

Page 19

Chapter 2: Board Components

2–11

MAX V CPLD 5M2210 System Controller

November 2013

Altera Corporation

Arria V GX Starter Board

Reference Manual

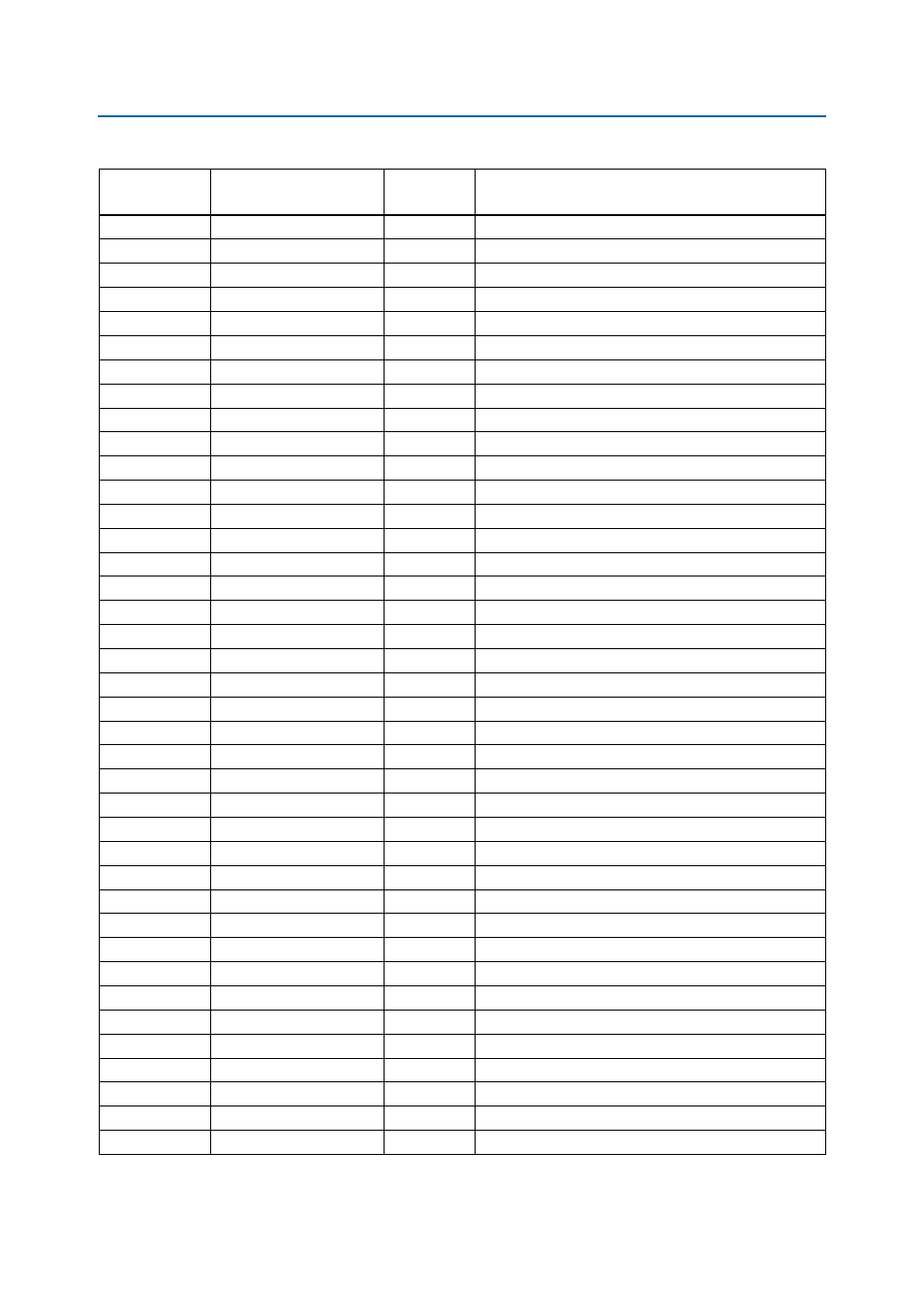

P10

MAX5_BEN0

2.5-V

FSM bus MAX V byte enable 0

R11

MAX5_BEN1

2.5-V

FSM bus MAX V byte enable 1

T12

MAX5_BEN2

2.5-V

FSM bus MAX V byte enable 2

N11

MAX5_BEN3

2.5-V

FSM bus MAX V byte enable 3

T11

MAX5_CLK

2.5-V

FSM bus MAX V clock

R10

MAX5_CSN

2.5-V

FSM bus MAX V chip select

M10

MAX5_OEN

2.5-V

FSM bus MAX V output enable

N10

MAX5_WEN

2.5-V

FSM bus MAX V write enable

E11

MAX_CONF_DONEN

2.5-V

On-board USB-Blaster II configuration done LED

A4

MAX_ERROR

2.5-V

FPGA configuration error LED

A6

MAX_LOAD

2.5-V

FPGA configuration active LED

M9

MAX_RESETN

2.5-V

MAX V reset push button

B10

MSEL0

2.5-V

FPGA mode select 0

B3

MSEL1

2.5-V

FPGA mode select 1

C10

MSEL2

2.5-V

FPGA mode select 2

C12

MSEL3

2.5-V

FPGA mode select 3

C6

MSEL4

2.5-V

FPGA mode select 4

B7

OVERTEMP

2.5-V

Temperature monitor fan enable

C7

PCIE_JTAG_EN

2.5-V

DIP switch to enable the PCI Express JTAG master

D12

PGM_CONFIG

2.5-V

Load the flash memory image identified by the PGM LEDs

B14

PGM_LED0

2.5-V

Flash memory PGM select indicator 0

C13

PGM_LED1

2.5-V

Flash memory PGM select indicator 1

B16

PGM_LED2

2.5-V

Flash memory PGM select indicator 2

B13

PGM_SEL

2.5-V

Toggles the PGM_LED[2:0] LED sequence

D5

SDI_RX_BYPASS

2.5-V

SDI equalization bypass

E8

SDI_RX_EN

2.5-V

SDI receive enable

D11

SDI_TX_EN

2.5-V

SDI transmit enable

R12

SECURITY_MODE

2.5-V

Reserved for future use

E7

SENSE_CS0N

2.5-V

Power monitor chip select

A5

SENSE_SCK

2.5-V

Power monitor SPI clock

D7

SENSE_SDI

2.5-V

Power monitor SPI data in

B6

SENSE_SDO

2.5-V

Power monitor SPI data out

D4

SI571_EN

2.5-V

Si571 programmable VCXO enable

R4

USB_CFG0

2.5-V

Reserved for future use

T4

USB_CFG1

2.5-V

Reserved for future use

P8

USB_CFG2

2.5-V

Reserved for future use

T7

USB_CFG3

2.5-V

Reserved for future use

N8

USB_CFG4

2.5-V

Reserved for future use

R8

USB_CFG5

2.5-V

Reserved for future use

Table 2–5. MAX V CPLD 5M2210 System Controller Device Pin-Out (Part 5 of 6)

Board

Reference (U15)

Schematic Signal Name

I/O Standard

Description