Altera Stratix V GX FPGA Development Board User Manual

Page 62

2–54

Chapter 2: Board Components

Memory

Stratix V GX FPGA Development Board

October 2014

Altera Corporation

Reference Manual

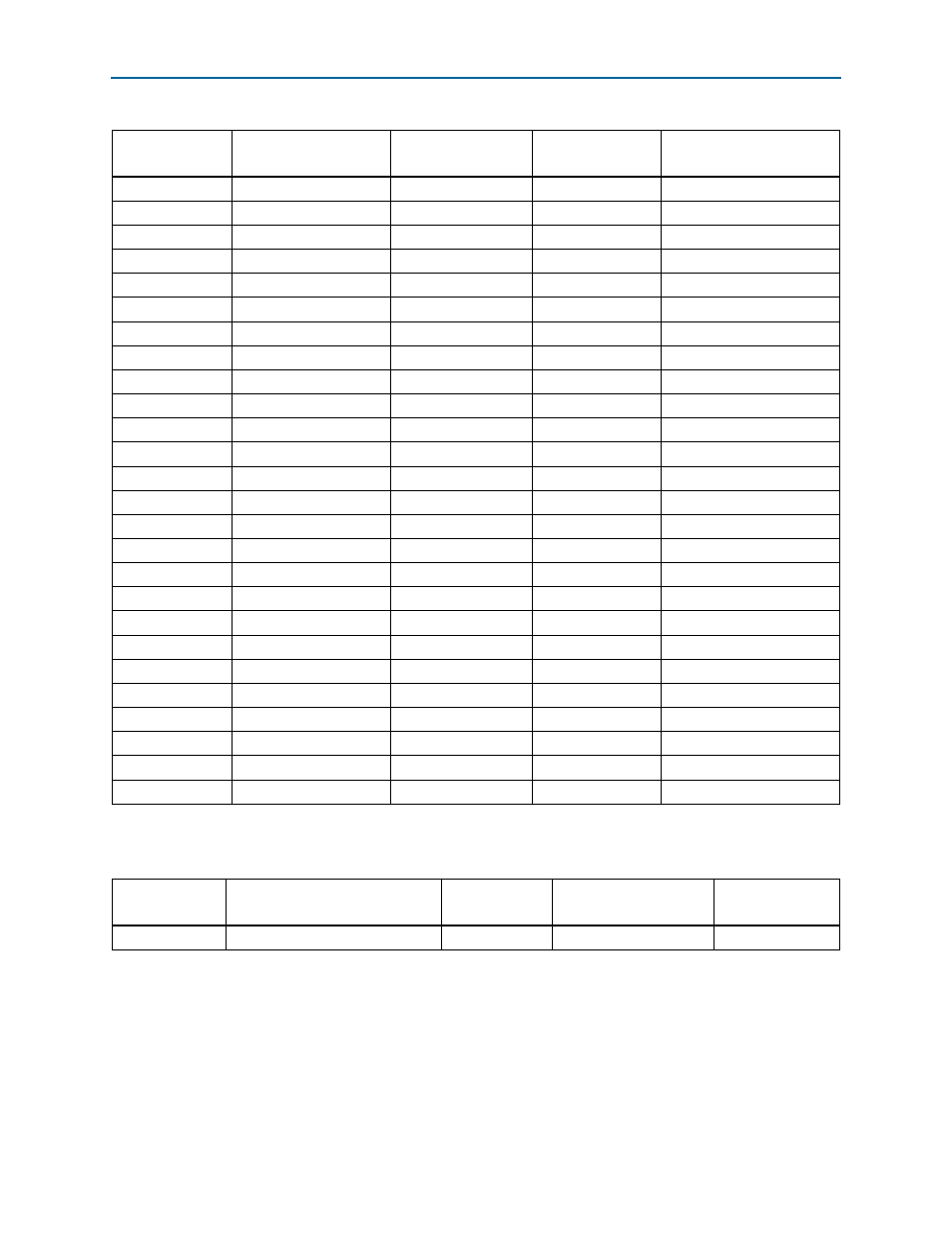

lists the RLDRAM II component reference and manufacturing information.

B10

RLDC_DQ0

1.8-V HSTL Class I

AW26

Write data

C10

RLDC_DQ1

1.8-V HSTL Class I

AN27

Write data

E10

RLDC_DQ2

1.8-V HSTL Class I

AN26

Write data

F10

RLDC_DQ3

1.8-V HSTL Class I

AM26

Write data

B3

RLDC_DQ4

1.8-V HSTL Class I

AV26

Write data

C3

RLDC_DQ5

1.8-V HSTL Class I

AU26

Write data

D3

RLDC_DQ6

1.8-V HSTL Class I

AU27

Write data

E3

RLDC_DQ7

1.8-V HSTL Class I

AT26

Write data

F3

RLDC_DQ8

1.8-V HSTL Class I

AT27

Write data

N10

RLDC_DQ9

1.8-V HSTL Class I

AC25

Write data

P10

RLDC_DQ10

1.8-V HSTL Class I

AC26

Write data

R10

RLDC_DQ11

1.8-V HSTL Class I

AD26

Write data

T10

RLDC_DQ12

1.8-V HSTL Class I

AE26

Write data

U10

RLDC_DQ13

1.8-V HSTL Class I

AF26

Write data

N3

RLDC_DQ14

1.8-V HSTL Class I

AA25

Write data

P3

RLDC_DQ15

1.8-V HSTL Class I

AG26

Write data

T3

RLDC_DQ16

1.8-V HSTL Class I

AG25

Write data

U3

RLDC_DQ17

1.8-V HSTL Class I

AH25

Write data

D10

RLDC_QK_N0

1.8-V HSTL Class I

AR27

Output data clock

R3

RLDC_QK_N1

1.8-V HSTL Class I

AK26

Output data clock

D11

RLDC_QK_P0

1.8-V HSTL Class I

AP27

Output data clock

R2

RLDC_QK_P1

1.8-V HSTL Class I

AJ26

Output data clock

F12

RLDC_QVLD

1.8-V HSTL Class I

AL26

Data valid

L1

RLDC_REFN

1.8-V HSTL Class I

AM22

Reference command

M1

RLDC_WEN

1.8-V HSTL Class I

AN22

Write enable

V2

RLDC_ZQ

1.8-V HSTL Class I

—

Output impedance control

Table 2–54. RLDRAM II Pin Assignments, Signal Names and Functions (Part 2 of 2)

Board Reference

(U20)

Schematic Signal Name

I/O Standard

Stratix V GX FPGA

Device Pin Number

Description

Table 2–55. RLDRAM II Component Reference and Manufacturing Information

Board Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

U20

533 MHz CIO RLDRAM II

Micron

MT49H32M18BM-18