Altera Stratix V GX FPGA Development Board User Manual

Page 32

2–24

Chapter 2: Board Components

Clock Circuitry

Stratix V GX FPGA Development Board

October 2014

Altera Corporation

Reference Manual

lists the oscillators, its I/O standard, and voltages required for the

development board.

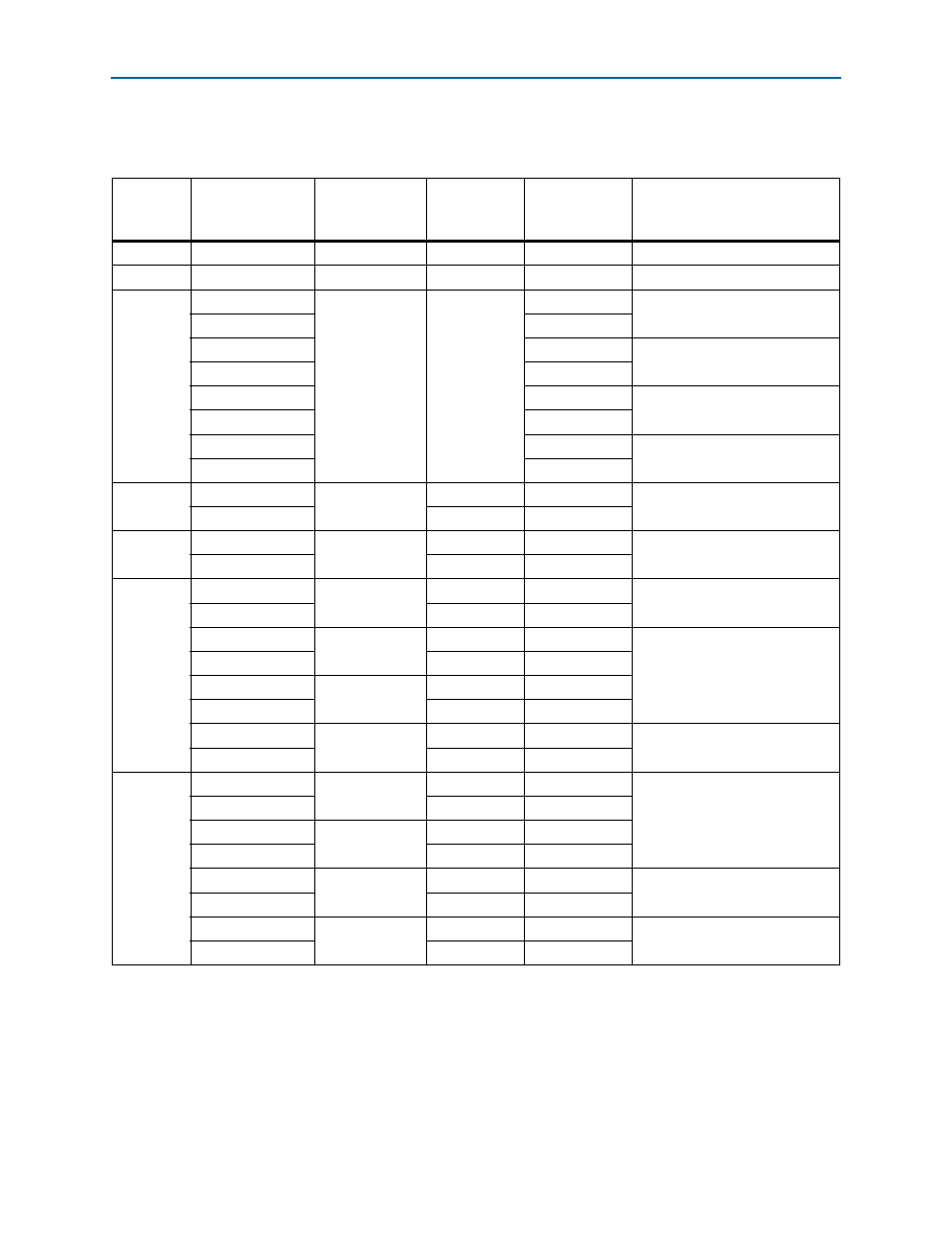

Table 2–22. On-Board Oscillators

Source

Schematic Signal

Name

Frequency

I/O Standard

Stratix V GX

FPGA Device

Pin Number

Application

X3

CLKIN_50

50.000 MHz

2.5V CMOS

AN6

Nios II and MAX V

X2

CLLK_CONFIG

100.000 MHz

2.5V CMOS

—

Fast FPGA configuration

X4

REFCLK1_QL0_P

100.000 MHz

LVDS

(fanout buffer)

AD33

PCI Express host/dual-XTL

REFCLK1_QL0_N

AD34

CLKINBOT_P0

AH22

Bottom edge

CLKINBOT_N0

AJ22

CLKINTOP_P0

J23

Top edge—DDR3

CLKINTOP_N0

J24

REFCLK4_QR2_P

V6

HSMC port B

REFCLK4_QR2_N

V5

X1

CLK_125_P

125.000 MHz

LVDS

AV29

10/100/1000 Ethernet

CLK_125_N

LVDS

AW29

X6

REFCLK5_QL2_P

148.500 MHz

LVDS

T33

HD-SDI video

REFCLK5_QL2_N

LVDS

T34

U46

CLKINTOP_P1

125.000 MHz

LVDS

N32

Top edge

CLKINTOP_N1

LVDS

M32

REFCLK4_QL2_P

282.500 MHz

LVDS

V34

QSFP

REFCLK4_QL2_N

LVDS

V35

REFCLK2_QL1_P

644.53125 MHz

LVDS

AB34

REFCLK2_QL1_N

LVDS

AB35

CLKINBOT_P1

125.000 MHz

LVDS

AF17

Bottom edge—memory

CLKINBOT_N1

LVDS

AG17

U38

REFCLK5_QR2_P

270.000 MHz

LVDS

T7

HSMC port B

REFCLK5_QR2_N

LVDS

T6

REFCLK2_QR1_P

625.000 MHz

LVDS

AB6

REFCLK2_QR1_N

LVDS

AB5

REFCLK1_QR0_P

156.250 MHz

LVDS

AD7

XAUI, 10GbE, HSMC port A

REFCLK1_QR0_N

LVDS

AD6

REFCLK0_QR0_P

100.000 MHz

LVDS

AF6

HSMC port A

REFCLK0_QR0_N

LVDS

AF5