Altera Stratix V GX FPGA Development Board User Manual

Page 21

Chapter 2: Board Components

2–13

Configuration, Status, and Setup Elements

October 2014

Altera Corporation

Stratix V GX FPGA Development Board

Reference Manual

MAX II CPLD EPM570GM100

The MAX II CPLD is dedicated to the on-board USB-Blaster II functionality. The

CPLD connects to the CY7C68013A USB 2.0 PHY device on one side and drives the

JTAG and System Console direct USB signals out the other side through the general

purpose I/O (GPIO) pins.

lists the I/O signals present on the MAX II CPLD EPM570GM100.

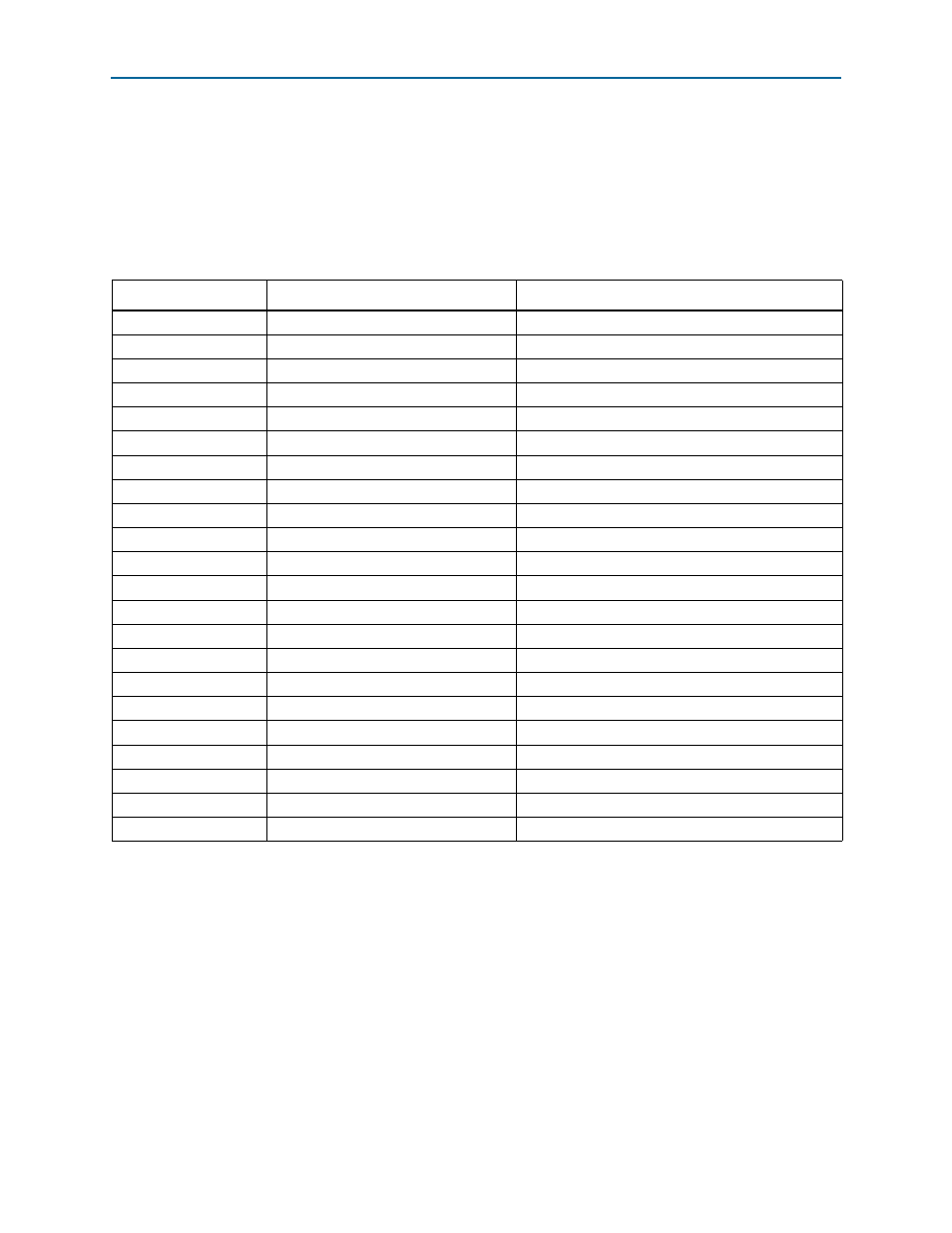

Table 2–7. MAX II CPLD EPM570GM100 On-Board USB-Blaster II I/O Signals

Schematic Signal Name

Type

Description

SC_RX

1.5-V CMOS output

USB system console receive LED

SC_TX

1.5-V CMOS output

USB system console transmit LED

JTAG_RX

1.5-V CMOS output

USB-Blaster II JTAG receive LED

JTAG_TX

1.5-V CMOS output

USB-Blaster II JTAG transmit LED

C_JTAG_TCK

2.5-V CMOS output

GPIO for on-board JTAG chain clock

C_JTAG_TMS

2.5-V CMOS output

GPIO for on-board JTAG chain mode

C_JTAG_TDI

2.5-V CMOS output

GPIO for on-board JTAG chain data in

C_JTAG_TDO

2.5-V CMOS input

GPIO for on-board JTAG chain data out

USB_CLK

3.3-V CMOS input

USB System Console clock

USB_OEn

1.5-V CMOS output

USB System Console FPGA output enable

USB_RESETn

1.5-V CMOS output

USB System Console reset

USB_DATA(7:0)

1.5-V CMOS inout (8 bits)

USB System Console FIFO data bus

USB_RDn

1.5-V CMOS output

USB System Console read from FIFO

USB_WRn

1.5-V CMOS output

USB System Console write to FIFO

USB_EMPTY

1.5-V CMOS input

USB System Console FIFO empty

USB_FULL

1.5-V CMOS input

USB System Console FIFO full

USB_ADDR(1:0)

1.5-V CMOS input/output

USB System Console address bus

USB_SCL

1.5-V CMOS input/output

USB System Console configuration clock

USB_SDA

1.5-V CMOS input/output

USB System Console configuration data

FACTORY_REQUEST

1.5-V CMOS output

Send FACTORY command

FACTORY_STATUS

1.5-V CMOS input

FACTORY command status

M570_CLOCK

1.5-V CMOS output

25-MHz input clock for FACTORY command