Altera Stratix V GX FPGA Development Board User Manual

Page 50

2–42

Chapter 2: Board Components

Components and Interfaces

Stratix V GX FPGA Development Board

October 2014

Altera Corporation

Reference Manual

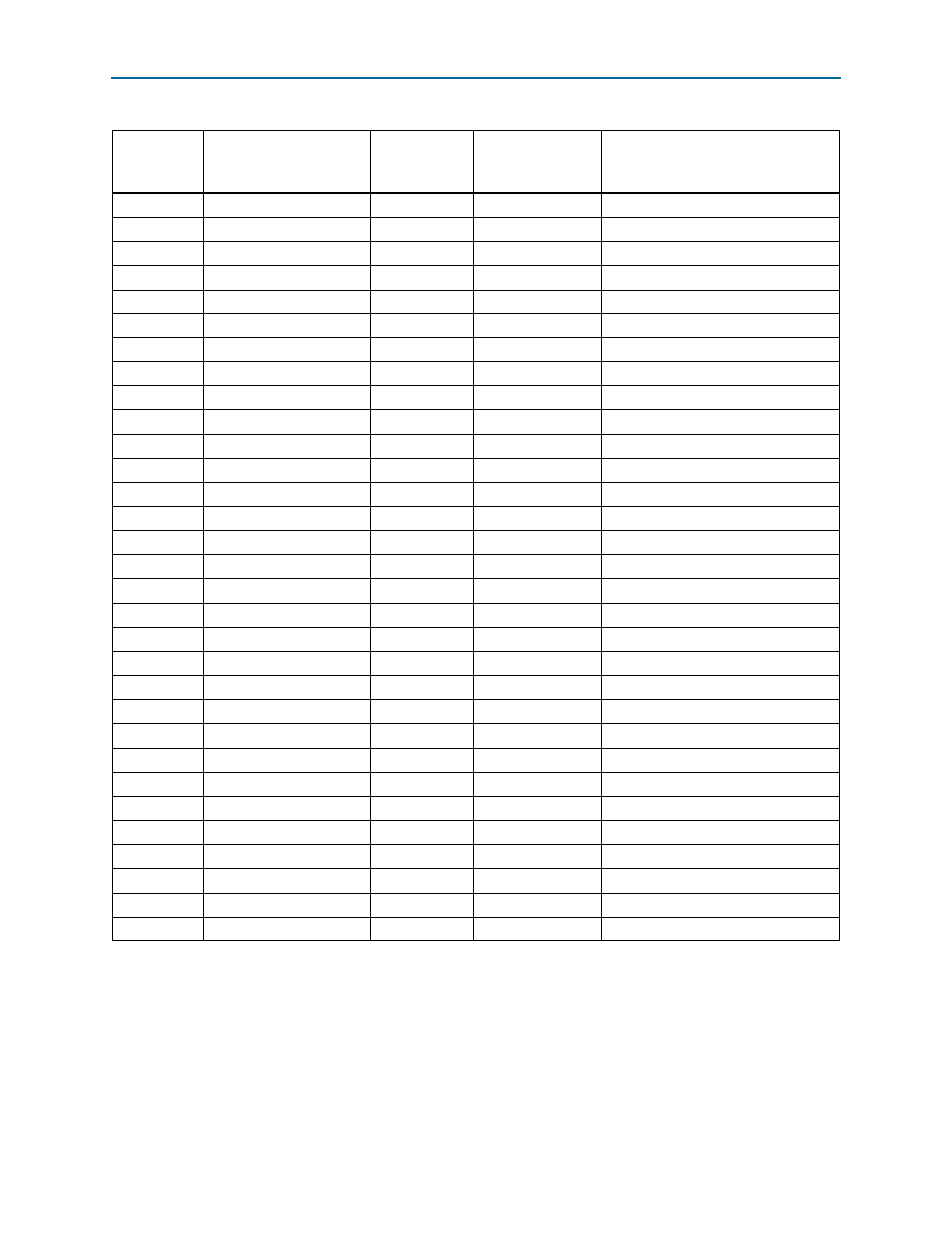

107

HSMB_DQ18

2.5-V CMOS

N14

Memory data bus

109

HSMB_DQ19

2.5-V CMOS

M14

Memory data bus

113

HSMB_DQ20

2.5-V CMOS

U14

Memory data bus

115

HSMB_DQ21

2.5-V CMOS

L15

Memory data bus

119

HSMB_DQ22

2.5-V CMOS

J14

Memory data bus

121

HSMB_DQ23

2.5-V CMOS

J15

Memory data bus

125

HSMB_DQ24

2.5-V CMOS

G15

Memory data bus

127

HSMB_DQ25

2.5-V CMOS

F14

Memory data bus

131

HSMB_DQ26

2.5-V CMOS

F15

Memory data bus

133

HSMB_DQ27

2.5-V CMOS

E14

Memory data bus

137

HSMB_DQ28

2.5-V CMOS

B14

Memory data bus

139

HSMB_DQ29

2.5-V CMOS

A14

Memory data bus

143

HSMB_DQ30

2.5-V CMOS

C14

Memory data bus

145

HSMB_DQ31

2.5-V CMOS

C15

Memory data bus

68

HSMB_DQS_N0

2.5-V CMOS

K13

Memory data strobe (negative)

92

HSMB_DQS_N1

2.5-V CMOS

C13

Memory data strobe (negative)

122

HSMB_DQS_N2

2.5-V CMOS

P14

Memory data strobe (negative)

146

HSMB_DQS_N3

2.5-V CMOS

D15

Memory data strobe (negative)

66

HSMB_DQS_P0

2.5-V CMOS

L13

Memory data strobe (positive)

90

HSMB_DQS_P1

2.5-V CMOS

D13

Memory data strobe (positive)

120

HSMB_DQS_P2

2.5-V CMOS

R14

Memory data strobe (positive)

144

HSMB_DQS_P3

2.5-V CMOS

E15

Memory data strobe (positive)

35

JTAG_TCK

2.5-V

AA31

JTAG clock

38

HSMB_JTAG_TDI

2.5-V

—

JTAG data input

37

HSMB_JTAG_TDO

2.5-V

—

JTAG data output

36

HSMB_JTAG_TMS

2.5-V

—

JTAG mode select

160

HSMB_PRSNTN

2.5-V

AU7

Presence detect signal

42

HSMB_RASN

2.5-V CMOS

P13

Memory address or command

34

HSMB_SCL

2.5-V CMOS

AL30

Management serial clock line

33

HSMB_SDA

2.5-V CMOS

AK30

Management serial data line

41

HSMB_WEN

1.4-V PCML

M17

Memory address or command

Table 2–41. HSMC Port B Pin Assignments, Schematic Signal Names, and Functions (Part 3 of 3)

Board

Reference

(J2)

Schematic Signal Name

I/O Standard

Stratix V GX FPGA

Device Pin Number

Description