Altera Arria V GZ Avalon-ST User Manual

Page 72

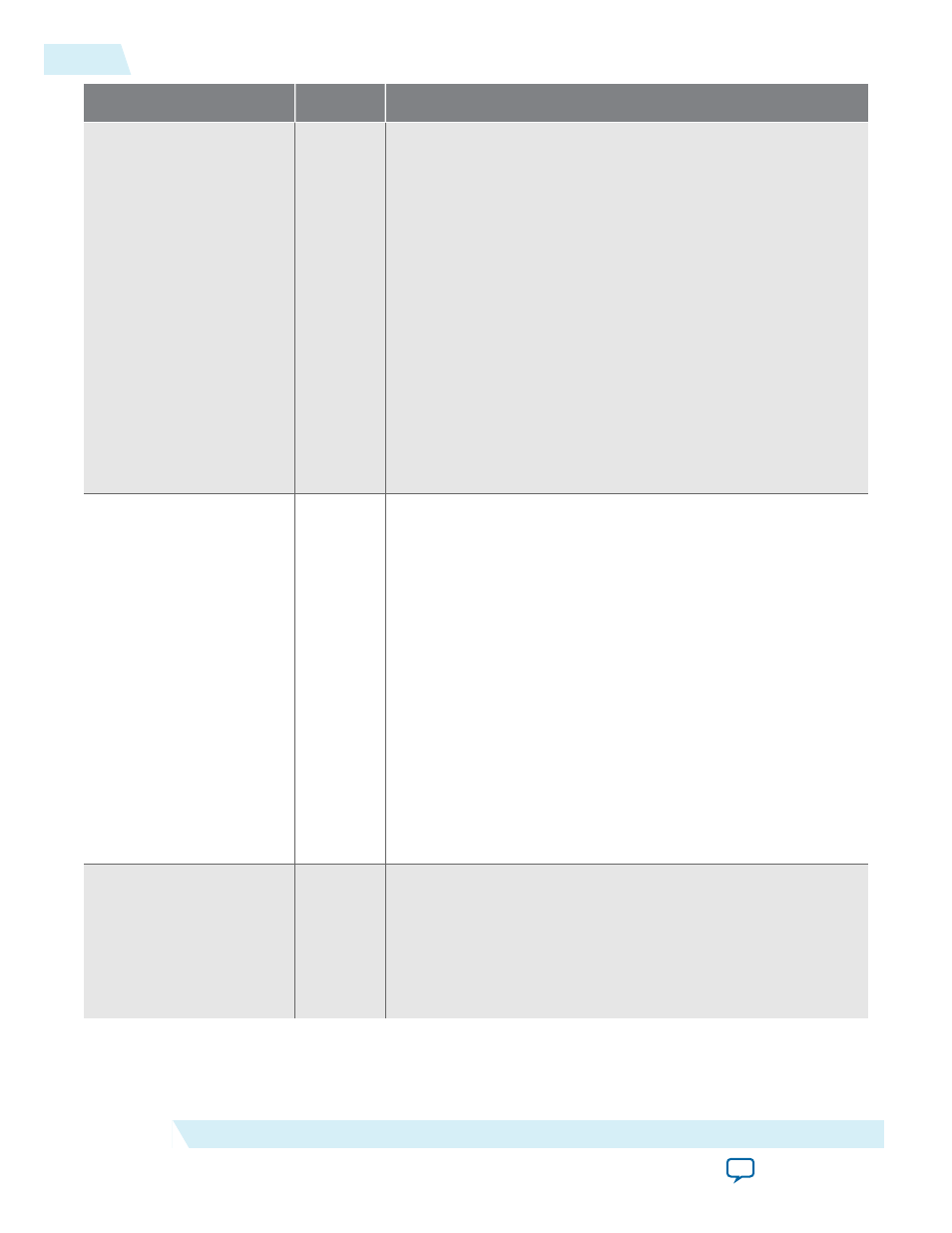

Signal

Direction

Description

tx_st_ready

Output

Indicates that the Transaction Layer is ready to accept data for

transmission. The core deasserts this signal to throttle the data

stream.

tx_st_ready

may be asserted during reset. The Applica‐

tion Layer should wait at least 2 clock cycles after the reset is

released before issuing packets on the Avalon-ST TX interface.

The

reset_status

signal can also be used to monitor when the

IP core has come out of reset.

If

tx_st_ready

is asserted by the Transaction Layer on cycle

is a ready cycle, during which

the Application Layer may assert

valid

and transfer data.

When

tx_st_ready

,

tx_st_valid

and

tx_st_data

are

registered (the typical case), Altera recommends a

readyLa-

tency

of 2 cycles to facilitate timing closure; however, a

readyLatency

of 1 cycle is possible. If no other delays are added

to the read-valid latency, the resulting delay corresponds to a

readyLatency

of 2.

tx_st_valid

Input

Clocks

tx_st_data

to the core when

tx_st_ready

is also

asserted. Between

tx_st_sop

and

tx_st_eop

,

tx_st_valid

must

not be deasserted in the middle of a TLP except in response to

tx_st_ready

deassertion. When

tx_st_ready

deasserts, this

signal must deassert within 1 or 2 clock cycles. When

tx_st_

ready

reasserts, and

tx_st_data

is in mid-TLP, this signal must

reassert within 2 cycles. The figure entitled64-Bit Transaction

Layer Backpressures the Application Layer illustrates the timing of

this signal.

For 256-bit data, when you turn on Enable multiple packets per

cycle, the bit 0 applies to the entire bus

tx_st_data[255:0]

. Bit

1 is not used.

To facilitate timing closure, Altera recommends that you register

both the

tx_st_ready

and

tx_st_valid

signals. If no other

delays are added to the ready-valid latency, the resulting delay

corresponds to a

readyLatency

of 2.

tx_st_empty[1:0]

Input

Indicates the number of qwords that are empty during cycles that

contain the end of a packet. When asserted, the empty dwords

are in the high-order bits. Valid only when

tx_st_eop

is asserted.

Not used when

tx_st_data

is 64 bits. For 128-bit data, only bit 0

applies and indicates whether the upper qword contains data. For

256-bit data, both bits are used to indicate the number of upper

5-20

Avalon-ST TX Interface

UG-01127_avst

2014.12.15

Altera Corporation

Interfaces and Signal Descriptions