Link capabilities – Altera Arria V GZ Avalon-ST User Manual

Page 48

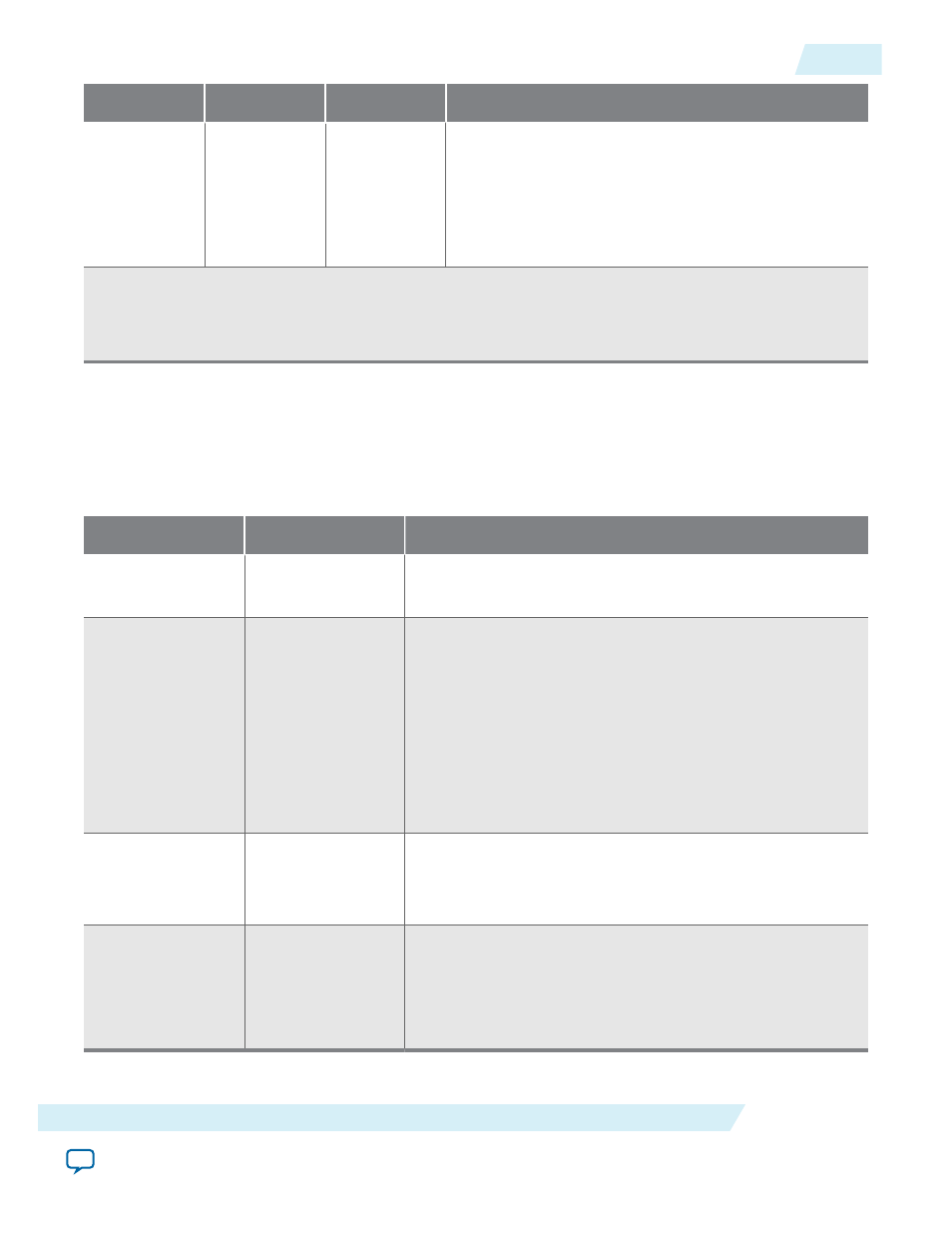

Parameter

Value

Default Value

Description

Track RX

completion

buffer

overflow on

the Avalon-

ST interface

On/Off

Off

When On, the core includes the

rxfx_cplbuf_ovf

output status signal to track the RX posted completion

buffer overflow status.

Note:

1. Throughout this user guide, the terms word, dword and qword have the same meaning that they have

in the PCI Express Base Specification. A word is 16 bits, a dword is 32 bits, and a qword is 64 bits.

Related Information

Link Capabilities

Table 4-7: Link Capabilities

Parameter

Value

Description

Link port

number

0x01

Sets the read-only value of the port number field in the

Link

Capabilities

register.

Data link layer

active reporting

On/Off

Turn On this parameter for a downstream port, if the

component supports the optional capability of reporting the

DL_Active state of the Data Link Control and Management

State Machine. For a hot-plug capable downstream port (as

indicated by the

Hot

Plug Capable

field of the

Slot

Capabilities

register), this parameter must be turned On.

For upstream ports and components that do not support this

optional capability, turn Off this option. This parameter is

only supported for the Arria V GZ Hard IP for PCI Express in

Root Port mode.

Surprise down

reporting

On/Off

When this option is On, a downstream port supports the

optional capability of detecting and reporting the surprise

down error condition. This parameter is only supported for

the Arria V GZ Hard IP for PCI Express in Root Port mode.

Slot clock

configuration

On/Off

When On, indicates that the Endpoint or Root Port uses the

same physical reference clock that the system provides on the

connector. When Off, the IP core uses an independent clock

regardless of the presence of a reference clock on the

connector.

UG-01127_avst

2014.08.18

Link Capabilities

4-11

Parameter Settings

Altera Corporation