Physical layer errors, Data link layer errors – Altera Arria V GZ Avalon-ST User Manual

Page 154

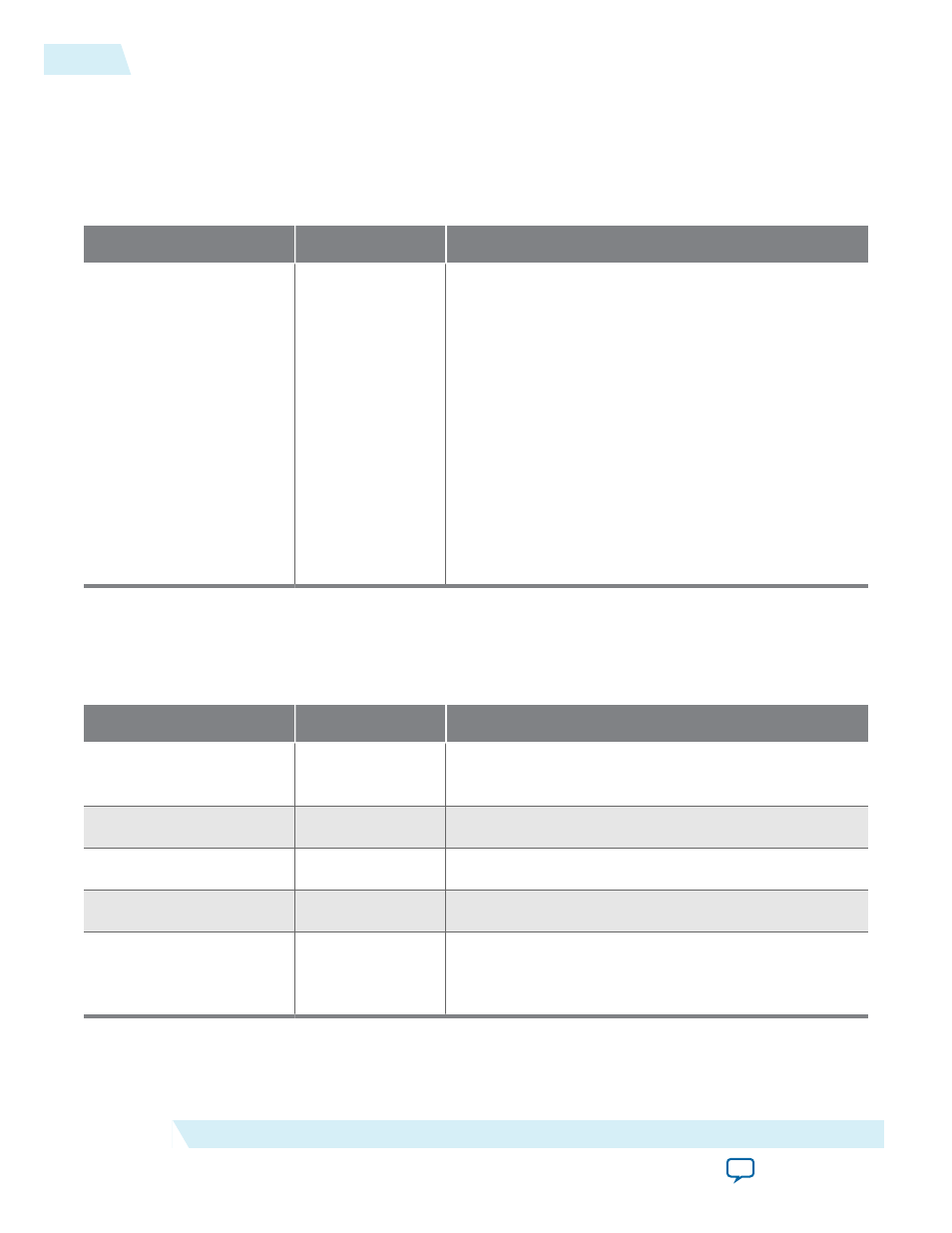

Physical Layer Errors

Table 9-2: Errors Detected by the Physical Layer

The following table describes errors detected by the Physical Layer. Physical Layer error reporting is optional in

the PCI Express Base Specification.

Error

Type

Description

Receive port error

Correctable

This error has the following 3 potential causes:

• Physical coding sublayer error when a lane is in L0

state. These errors are reported to the Hard IP block

via the per lane PIPE interface input receive status

signals,

rxstatus

using the

following encodings:

• 3'b100: 8B/10B Decode Error

• 3'b101: Elastic Buffer Overflow

• 3'b110: Elastic Buffer Underflow

• 3'b111: Disparity Error

• Deskew error caused by overflow of the multilane

deskew FIFO.

• Control symbol received in wrong lane.

Data Link Layer Errors

Table 9-3: Errors Detected by the Data Link Layer

Error

Type

Description

Bad TLP

Correctable

This error occurs when a LCRC verification fails or

when a sequence number error occurs.

Bad DLLP

Correctable

This error occurs when a CRC verification fails.

Replay timer

Correctable

This error occurs when the replay timer times out.

Replay num rollover

Correctable

This error occurs when the replay number rolls over.

Data Link Layer protocol Uncorrectable(fatal) This error occurs when a sequence number specified by

the Ack/Nak block in the Data Link Layer (

AckNak_Seq_

Num)

does not correspond to an unacknowledged TLP.

9-2

Physical Layer Errors

UG-01127_avst

2014.12.15

Altera Corporation

Error Handling